ch2-4LEDIT绘制nmos管版图

cadence实验:PMOS、NMOS设计步骤

PMOS、NMOS 版图设计尺寸参考说明:数字1、2、3……代表画版图时,第一层、第二层、第三层……或说成第一步、第二步、第三步……,一步一步做下来。

一、PMOS版图有关尺寸参考1、THIN (薄氧化层):与DIFF(扩散区/有源区)等价,在画版图时可以用DIFF代替。

长度3.4 宽度1.2 (默认单位um)2、GPOL Y:多晶硅导电层做mos管的栅极,可以用POL Y1代替,也可以做互连线。

长:2.4 宽:0.4 离有源区(即上面的THIN)左边缘1.5u ,比有源区上下各长出0.6u3、CONT:引线孔,连接金属与多晶硅/有源区,第一层金属的接点。

大小0.4*0.4 离有源区上边缘0.4 左边缘0.34、METAL1:第一层金属,用于水平布线,如电源和地,器件之间的连接必须依靠它。

大小:0.8*0.8 离CONT各0.25、THIN(或DIFF):大小1.0*1.0 离CONT各0.3 , 或离METAL1 各0.16、PPIMP (或PIMP):P型注入掩膜。

长:4.0 宽:1.8 离有源区上边缘0.3 ,离有源区左边缘0.37、NWELL:N阱,不仅用在制造P型器件,常在隔离的时候也看到它。

长6.5宽5.7 ,离PPIMP 左边缘1.2 ,离PPIMP 上边缘2.78、再另外做一个节点:CONT(0.4*0.4),METAL1(0.8*0.8),THIN (1.0*1.0)在已经画好图形的上方,CONT 离PPIMP 上端1.35 ,离NWELL 左端1.8 9、在新节点上加一个NPIMP(或NIMP):N型注入掩膜,大小为1.7*1.7 ,离THIN 各0.35二、NMOS版图有关尺寸参考1、THIN :长3.4 宽0.42、GPLOY :与PMOS 相同离有源区(即上面的THIN)左边缘1.5u ,比有源区上下各长出0.6u3、CONT :0.4*0.4 ,离有源区上边缘0.3 ,左边缘0.34、METAL1 :与PMOS 相同5、THIN :与PMOS 相同6、NPIMP :长4.0 宽1.6 离有源区上边缘0.3 ,离有源区左边缘0.37、再另外做一个节点:CONT(0.4*0.4),METAL1(0.8*0.8),THIN (1.0*1.0)在已画好图形的下方,CONT 离NPIMP 下端1.15 ,离NPIMP 左端0.6 8、在新节点上加一个PPIMP:大小1.7*1.7 离THIN 各0.35第三部分:画一个反相器时要做一个输入引脚1、GPOL Y:大小为1.6*1.6 (大小可以随意),离PMOS 的NWELL 下边缘0.7u(距离可以随意),此线框进入PMOS与NMOS 相连的GPOL Y 深度为0.2 。

使用L-Edit画反相器的布局图

(29)绘制电源线:由于反相器电路需要有Vdd 电源与GND 电源,电源 绘制是以Metal1图层表示,利用Metal1 将图中pmos 上方与nmos 下方 各绘制一个宽为39 个格点、高为5 个格点的电源图样,绘制后进行检 查,没有错误,如图所示。

(30)标出Vdd 与GND 节点:单击插入节点按钮 ,再到编辑窗口中用鼠 标左键拖曳出一个与上方电源图样重叠的宽为39 个格点、高为5 个格点 的方格后,将出现Edit Object(s)对话框,如图所示。

(18)引用nmos 组件:使ex11文件的Cell0为当前编辑窗口,选择 Cell—Instance 命令,打开Select Cell to Instance 对话框,可以看到 ,在组件列表中有Cell0,nmos 与pmos 这3 个组件,选择nmos 组 件再单击OK 按钮,可以看到编辑画面出现一个nmos 组件,

使用L-Edit画反相器的布局图

(1)打开L-Edit程序 (2)另存新文件:选择 File→Save As,重命 名,比如ex10(自己随意设定) (3)取代设定:选择 File→Replace Setup命 令,单击右侧的Browser,选择:\TannerEDA\LEdit11.1\samples\spr\example1\lights.tdb文 件,然后点击ok,会出现警告,按确定钮。

(10)设计规则检查:由于绘制的图样是要制作集

成电路的光罩图样,必须配合设计规则绘制图层, 才能确保流程时的效率。设计规则检查Tools—DRC 或按快捷按钮

(11)截面观察:利用L-Edit 的观察截面的功能,可观察该布局图设计出的 组件的制作流程与结果。选择Tools—Cross-Section 命令(或单击 按钮), 将打开Generate Cross-Section对话框, 单击其中的 Browser 按钮, 在弹 出的对话框中选择..\Tanner EDA\L-Edit11.1\samples\spr\example1\ lights.xst 文件,单击其中的Pick 按钮在编辑画面选择要观察的位置,再 单击Generat Cross-Section 对话框的OK 按钮。

MEMS 实验 使用L-Edit画PMOS布局图

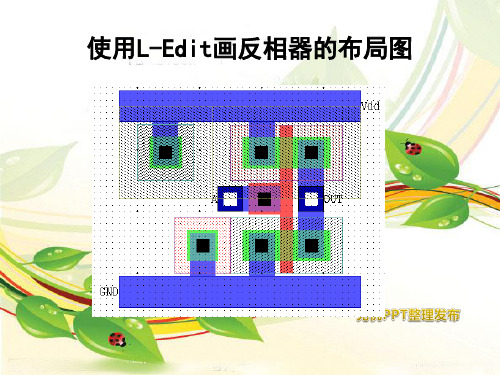

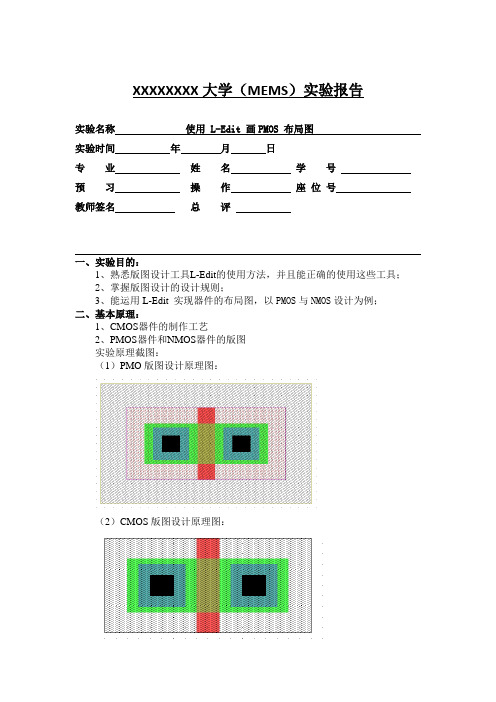

XXXXXXXX大学(MEMS)实验报告实验名称使用 L-Edit 画PMOS 布局图实验时间年月日专业姓名学号预习操作座位号教师签名总评一、实验目的:1、熟悉版图设计工具L-Edit的使用方法,并且能正确的使用这些工具;2、掌握版图设计的设计规则;3、能运用L-Edit 实现器件的布局图,以PMOS与NMOS设计为例;二、基本原理:1、CMOS器件的制作工艺2、PMOS器件和NMOS器件的版图实验原理截图:(1)PMO版图设计原理图:(2)CMOS版图设计原理图:3、设计版图时的注意事项:(1)L-Edit编辑环境是预设在P型基板上,故在P型基板上制作PMOS的第一步是需要做出N Well区,即需设定N阱区;然而对于NMOS则不需要N Well群区。

此外在设计版图时,需要将图绘制在原点之上,否则不利用版图截面的观察。

(2)改变图形大小的方法:“alt+鼠标拖动边框”;移动图形的方法“alt+鼠标拖动图形”;(3)绘制各图层之前需先通过Tools---DRC Setup查看对应的设计规则,从而选择确定图层的大小;绘制完一个图层都需DRC 进行设计规则检查;(4)各图层绘制无先后顺序的规定;(5)绘图时可适当使用“尺子”功能,以确保版图设计的对称性;清除图中的“尺寸”使用“View---Objects---Rules”或者选中后删除。

(6)对版图设计时,要注意时刻遵循设计规则,否则会出错误。

(7)对版图进行截面观察时,应注意选择好文件的路径,并且要设置好适当的界线位置。

三、实验内容及步骤:(1)打开 L-Edit 程序。

(2)另存新文件:选择 File---Save As命令,打开“另存为”对话框,在“保存在”下拉列表框中选择存储目录,在“文件名”文本框中输入新文件名称,例如:exp3。

(3)取代设定:选择File---Replace Setup命令,单击出现的对话框的From file 下拉列表右侧的 Browser按钮,择…:\LEdit83\Samples\SPR\example1\lights.tdb文件,再单击 OK 按钮,就可将 lights.tdb 文件的设定选择性应用在目前编辑的文件,包括格点设定、图层设定等。

使用 L-Edit 画PMOS 布局图

一、实验目的1、熟悉版图设计工具L-Edit 的使用方法;2、能运用L-Edit 实现器件的布局图;二、基本原理1、CMOS 器件的制作工艺2、PMOS 器件和NMOS 器件的版图PMOS 器件的版图NMOS 器件的版图3、L-Edit 使用的注意事项(1)L-Edit 编辑环境是预设在P 型基板上,故在P 型基板上制作PMOS 的第一步是需要做出N Well 区,即需设定N 阱区;(2)改变图形大小的方法:“alt+鼠标拖动边框”;移动图形的方法“alt+鼠标拖动图形”;(3)绘制各图层之前需先通过Tools---DRC Setup 查看对应的设计规则,从而选择确定图层的大小;绘制完一个图层都需DRC 进行设计规则检查;(4)各图层绘制无先后顺序的规定;(5 )绘图时可适当使用“尺子”功能:;清除图中的“尺寸”使用“View---Objects---Rules”;三、实验内容及步骤(1)打开L-Edit 程序。

(2)另存新文件:选择File---Save As 命令,打开“另存为”对话框,在“保存在”下拉列表框中选择存储目录,在“文件名”文本框中输入新文件名称,例如,exp3。

(3)取代设定:选择File---Replace Setup 命令,单击出现的对话框的From file 下拉列表右侧的Browser 按钮,选择…:\LEdit83\Samples\SPR\example1\lights.tdb 文件,再单击OK 按钮,就可将lights.tdb 文件的设定选择性应用在目前编辑的文件,包括格点设定、图层设定等。

(4)编辑组件:L-Edit 编辑方式是以组件(Cell)为单位而不是以文件(File)为单位的,每一个文件可有多个Cell,而每一个Cell 可表示一种电路布局图或说明,每次打开新文件时自动打开一个Cell 并将之命名为Cell0,其中,编辑画面中的十字为坐标原点。

(5)设计环境设定:选择Setup 命令,打开Design 对话框。

实验-用L-edit进行集成电路的设计

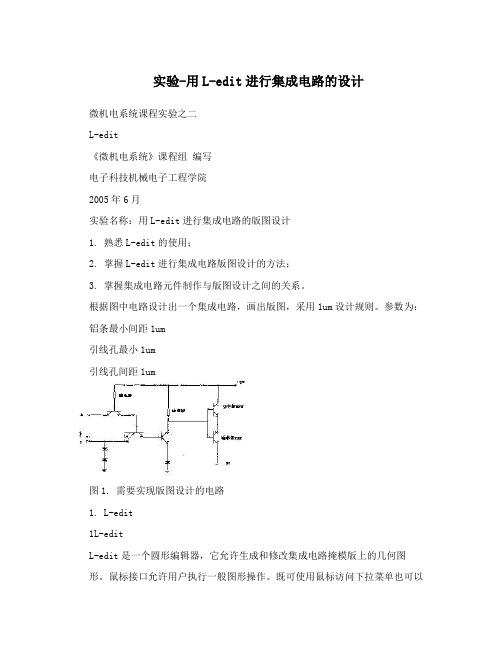

实验-用L-edit进行集成电路的设计微机电系统课程实验之二L-edit《微机电系统》课程组编写电子科技机械电子工程学院2005年6月实验名称:用L-edit进行集成电路的版图设计1. 熟悉L-edit的使用;2. 掌握L-edit进行集成电路版图设计的方法;3. 掌握集成电路元件制作与版图设计之间的关系。

根据图中电路设计出一个集成电路,画出版图,采用1um设计规则。

参数为:铝条最小间距1um引线孔最小1um引线孔间距1um图1. 需要实现版图设计的电路1. L-edit1L-editL-edit是一个圆形编辑器,它允许生成和修改集成电路掩模版上的几何图形。

鼠标接口允许用户执行一般图形操作。

既可使用鼠标访问下拉菜单也可以使用键盘来调用L-edit命令。

文件和单元使用文件、单元、连接器、掩模基元来描述布局设计,一个文件可以有任意多个单元组成,在典型设计中,这些单元可以有层次关系,也可以相互独立,单元可以包括任意数量的掩模基元和连接件,以及两者的组合,掩模单元由矩形、图、直线、多边形和技术层端口组成。

层次完全层次性的单元的连接件。

一个连接件是一个单元的“拷贝”,如果编辑连接单元,这种改变将反映到那个单元的所有连接件上。

L-edit对层次不作限制。

单元可以包含单元的连接件,被包含的单元又可以包含别的连接件,这样就形成了单元层次。

在层次结构中可以有任意级。

L-edit不能用于分离的层次结构,连接件和基元几何图形都可以存在于层次结构的任意级中的同一单元内。

单元设计L-edit是一个低层次的,全定制掩模编辑器,该编辑器不能执行层的自动转换。

层规划L-edit是一个高层规划工具。

用户可以选择要显示的连接件,它显示一个边框,中间显示单元名,也可以显示掩模几何图形。

使用内部隐藏时,可以操作用户设计的大型芯片级块,以获得所需要的层规划。

用户可使用用于操作基元的几何图形的命令。

文件格式L-edit能输出两种掩模布局交换格式(CIF, GDSII)以及Tanner Research公司的二进制数据库的格式TDB(Tanner Data Base),L-edit能够读取CIF (Caltech Intermediate Form)和TDB文件。

MEMS 实验 使用L-Edit画PMOS布局图

XXXXXXXX大学(MEMS)实验报告实验名称使用 L-Edit 画PMOS 布局图实验时间年月日专业姓名学号预习操作座位号教师签名总评一、实验目的:1、熟悉版图设计工具L-Edit的使用方法,并且能正确的使用这些工具;2、掌握版图设计的设计规则;3、能运用L-Edit 实现器件的布局图,以PMOS与NMOS设计为例;二、基本原理:1、CMOS器件的制作工艺2、PMOS器件和NMOS器件的版图实验原理截图:(1)PMO版图设计原理图:(2)CMOS版图设计原理图:3、设计版图时的注意事项:(1)L-Edit编辑环境是预设在P型基板上,故在P型基板上制作PMOS的第一步是需要做出N Well区,即需设定N阱区;然而对于NMOS则不需要N Well群区。

此外在设计版图时,需要将图绘制在原点之上,否则不利用版图截面的观察。

(2)改变图形大小的方法:“alt+鼠标拖动边框”;移动图形的方法“alt+鼠标拖动图形”;(3)绘制各图层之前需先通过Tools---DRC Setup查看对应的设计规则,从而选择确定图层的大小;绘制完一个图层都需DRC 进行设计规则检查;(4)各图层绘制无先后顺序的规定;(5)绘图时可适当使用“尺子”功能,以确保版图设计的对称性;清除图中的“尺寸”使用“View---Objects---Rules”或者选中后删除。

(6)对版图设计时,要注意时刻遵循设计规则,否则会出错误。

(7)对版图进行截面观察时,应注意选择好文件的路径,并且要设置好适当的界线位置。

三、实验内容及步骤:(1)打开 L-Edit 程序。

(2)另存新文件:选择 File---Save As命令,打开“另存为”对话框,在“保存在”下拉列表框中选择存储目录,在“文件名”文本框中输入新文件名称,例如:exp3。

(3)取代设定:选择File---Replace Setup命令,单击出现的对话框的From file 下拉列表右侧的 Browser按钮,择…:\LEdit83\Samples\SPR\example1\lights.tdb文件,再单击 OK 按钮,就可将 lights.tdb 文件的设定选择性应用在目前编辑的文件,包括格点设定、图层设定等。

LEdit绘制版图1

2020/3/29

图3.6 工艺参数设置标签页

②“Technology units”栏:用于设置工艺单位,共有6种: Microns(微米)、Mils(密耳)、Millimeters(毫米)、 Centimeters(厘米)、Inches(英吋)和Other(自定义单位)。 如选用Other选项,还需在其右边的填充框内输入自定义工艺单位 的名称(通常是Lambda)。

2020/3/29

2020/3/29

图3.10 图层设置对话框

3.3 文件与单元

在L-Edit中,设计是以TDB文件形式存在和保存。 TDB文件可以是版图文件,也可以是文本文件。TDB 文件由至少一个单元或多个单元组成。对于版图文件, 这些单元是以等级构造关系相互联系在一起。有些单 元只包含几何图形对象,称为基本单元,它们是独立 的单元;另一些单元则既可以包括几何图形,还可以 包含例化体。例化体是指在某个单元内对其他单元的 引用,就象调用子程序。这样在版图设计时就不必重 复绘制相同的版图结构,提高设计效率,同时还极大 地减少了设计所占的存储容量。

2020/3/29

4.图层设置 图层部分的设置包括有那些图层、图层的名称、对象

的电阻电容值、GDSⅡ的代号、CIF的名称、图样等 数据。执行Setup/ Layers子命令进入图层设置对话框, 如图3.10所示。对话框左边的图层列表框列出了当前 文件的图层,与图层定义区的次序是一致的。也可建 立新的图层(Add Layer)、删除原有的图层 (Delete Layer)和重新命名图层(Remane Layer), 还可安排各图层的先后顺序(Move Layer)。在窗口的 右边可以用来定义或是更改图层的名称,与各图层的 电气特性、布局方式、生成层的方式、图样等。若要 修改某层的参数时,只要选中右边列表框的某层,再 修改右边各标签页的数据即可。

CMOS反相器版图设计

XXXXXXX实验报告课程名称:集成电路设计实验名称:CMOS反相器版图设计学号姓名:指导教师评定:____________________________ 签名:_____________________________一、实验目的1、了解集成电路版图设计流程。

2、利用L-Edit 进行NMOSFET 版图设计。

3、利用L-Edit 进行CMOS反相器设计。

二、实验器材计算机一台,Tanner L-Edit软件三、实验原理CMOS 反相器由PMOS 和NMOS 晶体管组成,利用PMOS晶体管版图和NMOS 晶体管版图可以完成COMS反相器版图的设计。

四、实验步骤1、设计PMOS晶体管版图。

2、设计N MOS晶体管版图。

3、设计CMOS反相器版图:(1)启动版图编辑器L-Edit。

(2)新建文件。

新建一个Layout 文件,文件的设置信息可以从前面创建的文件中复制。

(3) 对文件进行重命名。

将L-Edit 编辑器默认的文件名Layout 改为Inverter。

(4) 设置格点与坐标。

格点与坐标的设定方式与创建PMOS 晶体管时设定的方法一致。

(5) 调用PMOS 和NMOS 晶体管作为例化单元。

使用Cell---Instance 命令来调用PMOS 单元。

在出现的Select Cell to Instance 对话框中,通过点击Browse按钮浏览到“MOS”文件,可以看到该文件下面有PMOS 和NMOS 两个单元,点击PMOS,然后点击“OK”,可以看到Inverter 文件cell0 单元的版图已经添加了PMOS 单元。

利用同样的方法,可以将NMOS 单元也添加进来。

(6) 连接PMOS 和NMOS 晶体管的栅极。

从CMOS 反相器电路可知,PMOS晶体管和NMOS 晶体管的栅极要连在一起作为反相器的输入端,所以在放置这两个晶体管的时候可以将两者的栅极对准,以便连接。

具体操作是,选择Layer的多晶硅(Poly)层和方框绘图工具后,在版图区域中画一个宽度与晶体管栅极相等的多晶硅矩形,如图1 所示。

L-Edit绘制版图

2013-7-13

3.设计参数设臵 在版图设计之前必须对有关参数进行设臵。 执行Setup/ Design子命令,进入设臵参数对 话框,如图3.6所示,共有6个标签页。 (1)“Technology(工艺参数)”标签页图 3.6 工艺参数设臵标签页 ①“Technology name”(工艺名称)栏:填 写设计所用的工艺名称。当要从一个文件拷贝 一个单元到另一个文件时,L-Edit将比较两个 文件所用的工艺是否相同。如果工艺不同,LEdit将显示警告信息。

图3.1 L-Edit窗

3.2 L-Edit的参数设置

在进行版图设计之前,首先要设定设计文件的 数据,如调色板、应用、设计、图层、特殊图 层、设计规则检查、标准单元库自动布局与连 线。

2013-7-13

1.调色板设臵 执行Setup Palette子命令弹出调色板设臵框, 如图3.4所示。L-Edit的色盘共有16种颜色设定, 每个颜色各有两种属性: (1)一个唯一的4位码; (2)RGB三种颜色的组合量。

2013-7-13

(2)选择新建版图文件之后,如果没有选择 任何设计文件(即选择<empty>),将产生一 个背景为灰色且只有一个New Layer图层的版 图窗口,该窗口未经任何参数设臵,经过设臵 也可达到满足要求的窗口。推荐使用TDB文件 新建版图文件的方法。 建立新的设计文件之后,可以使用File/Info子 命令设臵作者、组织名称、与文件数据等信息。

2013-7-13

(2)“General”标签页:提供使用者针对以 下事项进行设定。 ①Editing Options(编辑选项)栏:共有4个 选项,选中“Active-Push Rubberbanding” 选项表示在画圆形、方形时不必一直按着鼠标 的按钮,只要定义端点即可。例如,若要画一 个方形,先用鼠标左健定义方形的某一个角落, 再移到鼠标方形的对角位臵,然后再单击鼠标 左键,就可以完成方形的绘制。

集成电路版图或非门的版图实验

或非门版图实验

1、打开L-Edit程序

2、另存新文件:选择File---Save As命令,打开“另存为”对话框,在“保存在”

下拉表框中选择存储目录,在“文件名”文本框中输入新的文件名。

3、取代设定:选择File----Replace Setup命令,将出现一个对话框,单机Form file

下拉列表框右侧的Browser按钮,并选择light.tdb文件,在单击确定。

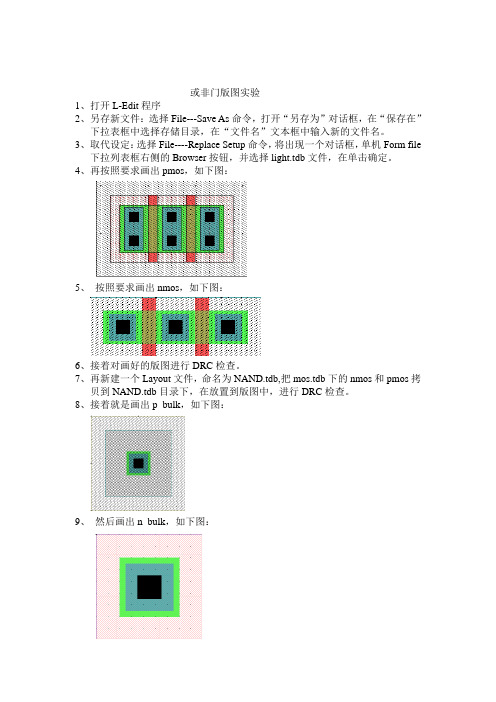

4、再按照要求画出pmos,如下图:

5、按照要求画出nmos,如下图:

6、接着对画好的版图进行DRC检查。

7、再新建一个Layout文件,命名为NAND.tdb,把mos.tdb下的nmos和pmos拷

贝到NAND.tdb目录下,在放置到版图中,进行DRC检查。

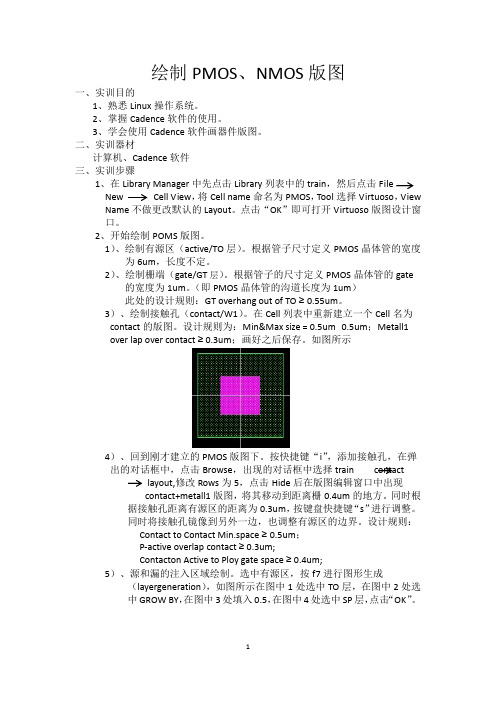

8、接着就是画出p_bulk,如下图:

9、然后画出n_bulk,如下图:

10、然后把各部分放到一张版图上,进行连接,然后进行DRC检查,如下图:

11、然后将图导出,生成网表文件,接着用T-spice打开,进行模拟。

对模拟

的量添加命令,如下:

.include "E:\Program Files\Tanner\tanner\TSpice70\models\ml2_125.md"

.tran/op 2n 80n method=bdf

.print tran v(A) v(B) v(Y)

vdc1 Vdd GND 5

vpulse1 A GND PULSE (0 5 0 2n 2n 8n 20n)

vpulse2 B GND PULSE (0 5 0 4n 4n 16n 40n)

仿真波形图如下:。

L-edit_版图绘制基础

选中图形,按住中间滚轮键,拖动选 中对象到你想移动到的地方

原位复制一个所选 择的对象

对选中对象进行上 下镜像操作

17

Company name

生成一个新 的cell

18

Company name

19

Company name

20

Company name

21

Company name

很多设备都不能直 接处理.tdb格式的文件, 这就需要一种通用性好 中间文件格式进行转换 ,如:gds文件。

30

Company name

Application为应用参数的设定: Workgroup用来指定设计组配置文件的路 径和名称;user用来指定设计者配置文件 的路径和名称。 General中编辑选项栏(Editing options) 中Paste to cursor指剪贴板上的图形粘贴到 鼠标指针上;Auto-panning指自动平移窗 口;Active-push rubberbanding指只需要定 义端点就可画出图形。 Toolbars中 Layer icon用于设置层定义区各 图标的尺寸,单位是像素;Drawing为设 定绘图模式。 Recently used file list:表示最近使用的文 件列表。 Keyboard用于设置键盘的热键。 Warning为警告框列表。 UPI为用户编程页面。

37

Company name

图形编辑:可以改变对象的大小和形状,在多边形中添加顶点,以及 对对象进行切割、合并和掏空等操作。 改变对象的大小和形状:在编辑图形前首先要选中对象,然后用鼠标 中键在对象的边或顶点的距离等于或小于编辑范围时按下,然后拖动鼠标 ,可以改变对象的大小和形状。编辑范围在设计参数对话框中设置。 多边形中添加顶点:把鼠标指针放在任意角多边形的边上,按下Ctrl 和MOVE-EDIT键,拖动鼠标,鼠标指针所在边上的点将变为一个新的顶 点,并随鼠标指针移动。

PMOS和NMOS版图

绘制PMOS、NMOS版图一、实训目的1、熟悉Linux操作系统。

2、掌握Cadence软件的使用。

3、学会使用Cadence软件画器件版图。

二、实训器材计算机、Cadence软件三、实训步骤1、在Library Manager中先点击Library列表中的train,然后点击FileNew Cell View,将Cell name命名为PMOS,Tool选择Virtuoso,View Name不做更改默认的Layout。

点击“OK”即可打开Virtuoso版图设计窗口。

2、开始绘制POMS版图。

1)、绘制有源区(active/TO层)。

根据管子尺寸定义PMOS晶体管的宽度为6um,长度不定。

2)、绘制栅端(gate/GT层)。

根据管子的尺寸定义PMOS晶体管的gate 的宽度为1um。

(即PMOS晶体管的沟道长度为1um)此处的设计规则:GT overhang out of TO ≥0.55um。

3)、绘制接触孔(contact/W1)。

在Cell列表中重新建立一个Cell名为contact的版图。

设计规则为:Min&Max size = 0.5um×0.5um;Metall1over lap over contact ≥ 0.3um;画好之后保存。

如图所示4)、回到刚才建立的PMOS版图下。

按快捷键“i”,添加接触孔,在弹出的对话框中,点击Browse,出现的对话框中选择train contactlayout,修改Rows为5,点击Hide后在版图编辑窗口中出现contact+metall1版图,将其移动到距离栅0.4um的地方。

同时根据接触孔距离有源区的距离为0.3um,按键盘快捷键“s”进行调整。

同时将接触孔镜像到另外一边,也调整有源区的边界。

设计规则:Contact to Contact Min.space ≥0.5um;P-active overlap contact ≥ 0.3um;Contacton Active to Ploy gate space ≥ 0.4um;5)、源和漏的注入区域绘制。

CMOS集成电路版图Tanner_L-Edit设计入门

集成电路版图设计入门主要内容:•版图设计概念;•CMOS VLSI制造工艺;•Tanner版图流程举例(反相器)。

版图设计概念定义:版图设计是创建工程制图(网表)的精确的物理描述过程,而这一物理描述遵守有制造工艺、设计流程以及通过仿真显示为可行的性能要求所带来的一系列约束。

双极集成电路版图设计MOS集成电路版图设计电压比较器运算放大器CMOS VLSI制造工艺(略)参见相关资料Tanner版图流程举例(反相器)集成电路设计近年来发展相当迅速,许多设计需要借助计算机辅助设计软件。

作为将来从事集成电路设计的工作人员,至少需要对版图有所了解,但是许多软件(如cadence)实在工作站上执行的,不利于初学者。

L-Edit软件是基于PC上的设计工具,简单易学,操作方便,通过学习,掌握版图的设计流程。

Tanner Pro简介:Tanner Pro是一套集成电路设计软件,包括S-EDIT,T-SPICE,W-EDIT,L-EDIT,与LVS ,他们的主要功能分别如下:1、S-Edit:编辑电路图2、T-Spice:电路分析与模拟3、W-Edit:显示T-Spice模拟结果4、L-Edit:编辑布局图、自动配置与绕线、设计规则检查、截面观察、电路转化5、LVS:电路图与布局结果对比设计参数的设置Setup>Design •该对话框共有六页,分别是:Technology(工艺参数)、Grid(网格参数)、Selection(选择参数)、Drawing(绘图参数)、Curves(曲线参数)、Xref files(外部交叉引用参数)•网格分为显示网格、鼠标网格(跳跃、平滑)、定位器网格设计规则的作用•设计规则规定了生产中可以接受的几何尺寸的要求和达到的电学性能。

•对设计和制造双方来说,设计规则既是工艺加工应该达到的规范,也是设计必循遵循的原则•设计规则表示了成品率和性能的最佳折衷设计规则的设置(一)、设计的类型•Minimum Width•Exact Width•Not Exist•Spacing•Surround•Overlap•Extension•Density(1)Minimum Width 该层上所有object在任意方向上的宽度(2) Exact width 该层上所有object在特定方向上的准确宽度(3)Not Exist在指定的层上,所有object都不能存在.这是唯一不含距离的规则(4)Spacing在指定的层上或者在指定的两层之间的object的最小间距(5)Surround 一个层上的物体,在每个方向上,被另一层上的物体至少要环绕x各单位(6)Overlap 一个层上的物体必须与另一个层上的物体交叠的最小尺寸。

L-edit及器件版图设计 ppt课件

62

PPT课件

Rendering工具栏: 设置产生图层的 显示特性。包括

object, port box, wire centerline的 设置。一般只设 置object。

L-EDIT的应用

63

PPT课件

Mode:绘图模式。 包括add(加), subtract(减), paint(涂色)。表 示和其它图层的逻 辑关系。Pass表示 第几次绘制。

GDS number:ຫໍສະໝຸດ 置图层 数等。Default wire setting:设 置线宽和连接点形状等 特性。

60

PPT课件

L-EDIT的应用

derivation工具栏:推 导产生图层

Draw和derived:选择 该图层是由绘制产生还 是由已有图层逻辑运算 产生。

61

PPT课件

L-EDIT的应用

58

PPT课件

L-EDIT的应用

Setup layers:图层设置

包含多种功能,是图层 文件建立和编辑的基础。 含有图层的建立,图层 的删除,图层的复制和 图层的重命名。

59

PPT课件

L-EDIT的应用

Electrical properties:电学 特性的设定。比如单位 面积电容的设定。一般 不设定。

Show edit vector:显示编 辑矢量。

Instance stretch :可伸缩 设置。选中可进行缓存 例体化拉伸等编辑

44

PPT课件

L-EDIT的应用

Toolbars 工具条

Use large button:选中后 编辑键图标将变大。

Layer icon:规定图层的 显示像素。

Drawing:选中all后可以 编辑所有角度图形,其 它选项为45度和90度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LOGO

第2单元绘制版图

主讲:赵琳娜

LOGO

2.4 绘制版图

绘制版图

CH2

LOGO 绘制版图

根据手中的0.25um 设计规则,画出反相器中NMOS 管的版图!(Tanner)

NMOS:1um/.25um PMOS:2um /.25um

LOGO

绘制版图

画版图时,要严格按照design rule 来画! 软件:tanner14.1 L-Edit

软件使用说明详见《集成电路版图设计入门》 好。

Come on !

LOGO Layer

零距离接触Tanner L-Edit !

LOGO

零距离接触Tanner L-Edit !

LOGO 零距离接触Tanner L-Edit !LOGO

零距离接触Tanner L-Edit !

LOGO 零距离接触Tanner L-Edit !LOGO

绘制版图

LOGO LVS

DRC 验证通过并不代表Layout 就完全正确了,极端的例子是Layout 中即使什么都没画,DRC 也不会报错,所以我们还需将Layout 和Schematic 作对比,看看是不是该画的器件都画上了,该连的线也都连对了,这样的检查叫LVS(Layout Vs. Schematic) LVS 验证需要的三个文件:

GDS2、网表文件(Netlist File )和LVS 命令文件

LOGO

绘制版图——DRC 检查

LOGO 绘制版图——DRC 检查LOGO

绘制版图

LOGO DRC 检查LOGO

DRC 检查

LOGO DRC 检查LOGO

画Schematic ,提取网表文件

1)网表文件(Netlist File )

1.

LOGO 画Schematic ,提取网表文件LOGO

画Schematic ,提取网表文件

LOGO

画Schematic ,提取网表文件C:\Users\bm\Documents\Tanner EDA\Tanner Tools v15.0\Designs\RingVCO\RingVCO.tanner

LOGO

画Schematic ,提取网表文件

LOGO 画Schematic ,提取网表文件

i

LOGO

画Schematic ,提取网表文件

LOGO 画Schematic ,提取网表文件LOGO

画Schematic ,提取网表文件

LOGO 画Schematic ,提取网表文件LOGO

导出的网表文件

LOGO GDS2LOGO

GDS2

LOGO GDS2LOGO

GDS2

LOGO LVS LOGO

LVS

LOGO LVS LOGO

LVS

LOGO LVS

LOGO

LVS

LOGO LVS LOGO

LVS

LOGO 把网表文件里面的nmos W 改为2um

LOGO

输出文件为inv.out

打开inv.out 文件

LOGO LVS 验证结果LOGO

LVS 验证结果

LOGO

LVS

如果LVS 没有通过,这时需要查看LVS 报告——*.out 。

报告会反映出Layout 和Netlist 不一致的地方。

部分lvs 报告:

Device Cell1.spc Cell0.spc Status ------------------------------------------------------------M_PMOS 1 1M_NMOS 1 1

------------------------T otal elements 2 2T otal nodes 4 4

Warning: Parametric mismatch between M_NMOS elements

Cell1.spc: M1: W=2u

Cell0.spc: MNMOS_1: W=1u

LOGO

LVS 常见错误

虽然LVS 错误的原因五花八门,但大抵可以分为下面几类:

LOGO LVS 常见错误LOGO

LVS 常见错误

LOGO LVS 常见错误LOGO

LVS 常见错误

LOGO LVS 常见错误LOGO

LVS 常见错误

LOGO LVS 常见错误LOGO

LVS 常见错误

LVS常见错误

LOGO LOGO。