利用VHDL实现(2,1,2)卷积码编码

vhdl中所使用的运算符

整数相除取余数

MOD

整数相除取商

-

取2的补码

ABS

取绝对值

VHDL中所使用的运算符

表1设定运算符

信号的设定

<=

变量的设定

=

表2关系运算符

等于

=

大于

>

小大于等于

>=

左移(原MSB移入LSB)

ROR

循环右移(原LSB移入MSB)

SLL

逻辑左移(0移入LSB)

SRL

逻辑右移(0移入MSB)

SLA

算数左移(原LSB保留)

SRA

算数右移(原MSB保留)

表4逻辑运算符

假设A、B为输入,Z为输出

AND

与

OR

或

NOT

非

NAND

与非

NOR

或非

XOR

异或

XNOR

同或

表5算数运算符

+加

A+ B

-减

A - B

*乘

A.B

/除

A/B

**次方

AB

-批注

Example

:声明使用

=>对应

&串接

Z <= A&B

表6其他运算符

vhdl中所使用的运算符设定运算符信号的设定关系运算符等于数值移位运算符rol循环左移原msb移入lsbror循环右移原lsb移入msbsll逻辑左移0移入lsbsrl逻辑右移0移入msbsla算数左移原lsb保留sra算数右移原msb保留逻辑运算符假设ab为输入z为输出批注example声明使用对应其他运算符rem整数相除取余数mod整数相除取商的补码abs取绝对值

基于VHDL的卷积码编解码器的设计报告

长沙理工大学《通信电路EDA》课程项目报告系别计通系专业通信工程班级通信1203班指导教师单树民项目组组长历洋学号201254080312 项目组成员刘鼎新学号201254080330 项目组成员陈士怡学号201254080324 项目组成员侯耀文学号201254080323完成日期2014年11月5日目录1 引言 (3)1.1项目背景 (3)2 卷积码编解码器的结构概述 (4)2.1 卷积码编码器的结构 (4)2.2 卷积译码器的结构 (4)3 卷积码编解码器的VHDL设计 (5)3.1 VHDL设计的优点与设计方法 (5)3.2 卷积码编解码器的VHDL实现 (6)3.2.1 卷积编解码器顶层建模的VHDL描述 (7)3.2.2 用MAX+PLUSⅡ编译后生成的编解码器图形符号错误!未定义书签。

3.2.3 卷积编解码器VHDL仿真波形 (9)4 后记 (11)基于VHDL的卷积码编解码器的设计1 引言1.1项目背景现代数字通信有两个基本的理论基础,即信息论和纠错编码理论,它们几乎是同时在第二次世界大战结束后不久诞生的。

前者首先由Shannon以他的不朽名著“通信的数学理论”为标志建立起来的,而后者则以Hamming的经典著作“纠错和检错编码”为代表。

Shannon信息论主要讨论信息的度量,以及对于信息表示和信息传输的基本限制。

信道编码定理告诉我们,只要信息传输速率小于信道容量,则信息传输可以以任何小的错误概率进行。

但是,Shannon信息论并没有告诉我们如何去实现这一点。

Hanmming提出的纠错编码理论正是为了解决这个问题。

科学技术的发展使人类跨入了高度发展的信息化时代。

在政治、军事、经济等各个领域,信息的重要性不言而喻,有关信息理论的研究正越来越受到重视。

20世纪50年代信息论在学术界引起了巨大的反响。

20世纪60年代信道编码技术有了较大进展,成为信息论的又一重要分支。

信道编码技术把代数方法引入到纠错码的研究,使分组码技术的发展到了高峰,找到了大量可纠正多个错误的码,而且提出了可实现的译码方法。

通信综合课程设计 卷积码的实现与仿真

文章标题:深度解析通信综合课程设计中卷积码的实现与仿真引言:通信综合课程设计是通信工程领域的重要教育环节,而卷积码作为其中的重要内容之一,其实现与仿真更是学生们需要深入了解和掌握的技能。

本文将从简到繁地讨论通信综合课程设计中卷积码的实现与仿真,帮助读者更好地理解和掌握这一重要内容。

第一部分:通信综合课程设计概述1.1 通信综合课程设计的重要性在通信工程领域,通信综合课程设计是学生将在实际工作中常常用到的实践环节,通过这一环节,学生们可以将所学的理论知识应用到实际项目中,提高实践能力和解决问题的能力。

1.2 通信综合课程设计的内容概述通信综合课程设计内容丰富多样,包括调制解调、信道编码、卷积码、纠错码等多个主题,而卷积码的实现与仿真是其中的重要部分之一。

第二部分:卷积码的基本原理2.1 卷积码的定义卷积码是一种线性时不变系统(LTI)编码器,在通信系统中起到纠错码的作用。

2.2 卷积码的编码和解码原理通过引入时延、存储元素和加法器,实现对输入序列进行编码;而解码过程则是通过译码器进行,根据输入序列和已知的编码规则进行解码。

第三部分:通信综合课程设计中卷积码的实现3.1 卷积码的软件实现在通信综合课程设计中,学生们可以利用MATLAB等软件工具,编写程序实现卷积码的编码和解码过程,从而加深对卷积码原理的理解。

3.2 卷积码的硬件实现除了软件实现,通信综合课程设计中也常常涉及到卷积码的硬件实现,学生们可以通过FPGA等硬件开发评台,实现卷积码的编码和解码过程。

第四部分:通信综合课程设计中卷积码的仿真4.1 仿真环境的建立在通信综合课程设计中,学生们需要建立仿真环境,包括信道模型、信号源、噪声源等,以便对卷积码的性能进行评估。

4.2 仿真结果的分析通过仿真实验,学生们可以得到卷积码在不同信噪比下的误码率曲线等性能参数,从而对卷积码的性能有更深入的了解。

结论:通过本文的深入讨论,相信读者已经对通信综合课程设计中卷积码的实现与仿真有了更深入的理解。

毕业设计:基于VHDL的循环码编译码器的设计

毕业设计报告(论文)报告(论文)题目:基于VHDL的循环码编译码器的设计作者所在系部:电子工程系作者所在专业:通信工程作者所在班级: B08232作者姓名:作者学号:指导教师姓名:完成时间: 2012年 6月15日北华航天工业学院教务处制本科生毕业设计(论文)原创性及知识产权声明本人郑重声明:所呈交的毕业设计(论文)基于VHDL的循环码编译码器的设计是本人在指导教师的指导下,独立进行研究工作取得的成果。

除文中已经注明引用的内容外,本设计(论文)不含任何其他个人或集体已经发表或撰写过的作品或成果。

对本设计(论文)的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

因本毕业设计(论文)引起的法律结果完全由本人承担。

本毕业设计(论文)成果归北华航天工业学院所有。

本人遵循北华航天工业学院有关毕业设计(论文)的相关规定,提交毕业设计(论文)的印刷本和电子版本。

本人同意北华航天工业学院有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;可以采用影印、缩印、数字化或其它复制手段保存论文;在不以营利为目的的前提下,可以公布非涉密毕业设计(论文)的部分或全部内容。

特此声明毕业设计(论文)作者:指导教师:年月日年月日摘要在本次设计中,使用Quartus II 7.0为系统开发平台,硬件描述语言VHDL为主要设计手段,以可编程逻辑器件为实现载体,设计方案中,从循环码编译码的原理出发,论证了BCH码编译码系统的设计方案,并利用VHDL语言加以实现。

所设计的系统可以完成BCH码编码以及两位错码的纠错译码。

依据设计方案和设计平台完成了程序编写和程序调试,通过运行程序及时序波形的仿真有效验证了设计的正确性,初步实现了设计目标。

关键词 VHDL BCH码编码器译码器AbstractThis design takes the Quartus II 7.0 as the system development platform, and takes hardware description language VHDL as the main design means. It also uses programmable logic devices for the realization of the carrier。

vhdl 四输入表决器 二位二进制乘法器 一位二进制全减器等源代码及仿真波形

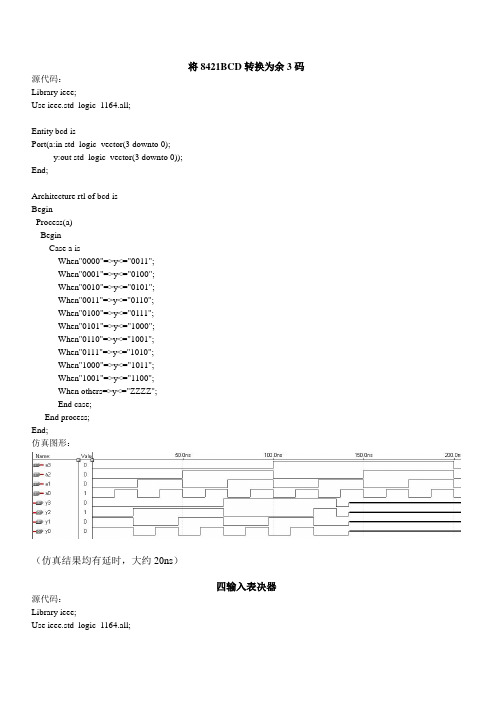

将8421BCD转换为余3码源代码:Library ieee;Use ieee.std_logic_1164.all;Entity bcd isPort(a:in std_logic_vector(3 downto 0);y:out std_logic_vector(3 downto 0));End;Architecture rtl of bcd isBeginProcess(a)BeginCase a isWhen"0000"=>y<="0011";When"0001"=>y<="0100";When"0010"=>y<="0101";When"0011"=>y<="0110";When"0100"=>y<="0111";When"0101"=>y<="1000";When"0110"=>y<="1001";When"0111"=>y<="1010";When"1000"=>y<="1011";When"1001"=>y<="1100";When others=>y<="ZZZZ";End case;End process;End;仿真图形:(仿真结果均有延时,大约20ns)四输入表决器源代码:Library ieee;Use ieee.std_logic_1164.all;Entity bjq isPort(i:in std_logic_vector(3 downto 0);f:out std_logic);End;Architecture nm2 of bjq isBeginProcess(i)Begincase i isWhen"0000"=>f<='0';When"0001"=>f<='0';When"0010"=>f<='0';When"0011"=>f<='0';When"0100"=>f<='0';When"0101"=>f<='0';When"0110"=>f<='0';When"0111"=>f<='1';When"1000"=>f<='0';When"1001"=>f<='0';When"1010"=>f<='0';When"1011"=>f<='1';When"1100"=>f<='0';When"1101"=>f<='1';When"1110"=>f<='1';When"1111"=>f<='1';When others=>f<='Z';End case;End process;End;仿真图形:2位二进制相乘电路源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity multi isport(A,B:in std_logic_vector(1 downto 0);F:out std_logic_vector(3 downto 0));end;architecture bhv of multi isbeginprocess(A,B)beginif(A="01" and B="01" )thenF<="0001";elsif(A="01" and B="10")thenF<="0010";elsif(A="01" and B="11")thenF<="0011";elsif(A="10" and B="01")thenF<="0010";elsif(A="10" and B="10")thenF<="0100";elsif(A="10" and B="11")thenF<="0110";elsif(A="11" and B="01")thenF<="0011";elsif(A="11" and B="10")thenF<="0110";elsif(A="11" and B="11")thenF<="1001";elseF<="0000";end if;end process;end;仿真图形:一位二进制全减器源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity subtracter isport(A,B,Ci:in std_logic;F,Co:out std_logic);end;architecture bhv of subtracter isbeginprocess(A,B,Ci)beginif(A='0' and B='0' and Ci='0')thenF<='0';Co<='0';elsif(A='0' and B='0' and Ci='1')thenF<='1';Co<='1';elsif(A='0' and B='1' and Ci='0')thenF<='1';Co<='1';elsif(A='0' and B='1' and Ci='1')thenF<='0';Co<='1';elsif(A='1' and B='0' and Ci='0')thenF<='1';Co<='0';elsif(A='1' and B='0' and Ci='1')thenF<='0';Co<='0';elsif(A='1' and B='1' and Ci='0')thenF<='0';Co<='0';elseF<='1';Co<='1';end if;end process;end;仿真图形:开关控制电路源代码:Library ieee;Use ieee.std_logic_1164.all;Entity switch_control isPort(a,b,c:in std_logic;y:out std_logic);End;Architecture nm5 of switch_control isBeginProcess(a,b,c);V ariable comb:std_logic_vector(2 downto 0);BeginComb:=a&b&c;Case comb isWhen"000"=>y<='0';When"001"=>y<='1';When"011"=>y<='0';When"010"=>y<='1';When"110"=>y<='0';When"111"=>y<='1';When"101"=>y<='0';When"100"=>y<='1';When others=>y<='X';End case;End process;End;仿真图形:。

vhdl编程实例

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

基于FPGA的卷积码编译码器

2.3.2定时与控制 由时钟控制,每个时钟输入一位,每两个时钟输出一位, 称为一个译码周期。在每个译码周期的前一个时钟周期内完 成“加”,此时译码状态为“0”;在后一个时钟周期内完成“比 和选”,译码状态为“l”。 2.3.3支路量度计算 由于(2,l,3)卷积码的形式已经固定,因此,可以事先把 支路量度表做好。如表1所示。译码器工作时可根据输入通 过查表得到“比前路径长度”的增加值,暂存到addi_j中,而 后统一加入“比前路径长度”chni_j中。 2.3.4路径量度和译码路径的更新与存储 在到达同一状态的两条路径中选取路径长度较小的作 为幸存路径。即在chnk_O和chnk_1中选择较小的存入

第19卷

V01.19

第8期

No.8

电子设计工程

Electronic Design Engineering

2011年4月

Apr.2011

基亏FPGA的卷积码编译码器

张有志I s张鹞2

(1.山东凯文科技职业学院山东济南250200;2.北京邮电大学信息与通信工程学院。北京100876) 摘要:基于卷积码的编译码原理,使用VHDL语言和FPGA芯片设计并实现了(2,1。3)卷积码编译码器。其中译码器 设计采用“截尾”的Viterbi译码算法,在支路量度计算、路径量度和译码路径的更新与存储以及判决与输出等环节的 实现中采取了若干有效措施,节省了存储空间,提高了设计性能。最后通过仿真验证了设计的正确性与合理性。 关键词:FPGA;卷积码;编译码器;Viterbi译码器;VHDL

and decoder which is designed by tail-biting representing branch metric,path

resources

运用VHDL实现数字信号处理

运用VHDL实现数字信号处理刘玉钦1吴国强2(中国人民解放军94647部队福州 350026)摘要:本文在综合多种数字信号系统设计方式优缺点的基础上,重点介绍用VHDL[Very High Speed Integrated Circuit (VHSIC) Hardware Description Language]语言在硬件芯片FPGA/CPLD上进行数字信号处理,设计移位相加硬件乘法器,实现快速乘法功能,并以Altera公司的ACEX1K系列产品作为硬件,将Max+plusⅡ软件作为开发工具,进行设计编码、功能仿真和硬件测试。

关键字:乘法器 硬件描述语言 数字信号处理中图分类号:TN812 文献标识码: BDigital Signal Process Basing on VHDLLiu Yuqin1Wu Guoqiang2(The 94647 of the PLA Fuzhou, 350026)Abstract:This paper is based on summarizing several kinds of advantage as well as disadvantage of system designs in digital signal process and it mainly introduces the digital signal process on the hardware chip FPGA/CPLD using VHDL[Very High Speed Integrated Circuit (VHSIC) Hardware Description Language], the realization of the high-speed multiplier, and Using the Max+plusⅡsoftware as the exploiting tool to design program, function simulate and hardware test with ACEX1K series the product of Altera company.Keywords:Multiplier Hardware Description Language (HDL) Digital Signal Process数字信号处理(DSP)技术具有广泛的用途,如在图像处理、数字通信、雷达等方面发挥着重要的作用。

基于VHDL汉明码编译码器的设计与实现毕业论文

基于VHDL汉明码编译码器的设计与实现目录摘要 1第一章绪论 31.1研究背景与选题意义 31.2研究目标与主要工作 31.3论文的内容安排 4第二章汉明码及汉明码编译原理 42.1 纠错编码的基本原理 42.1.1 分组码基本原理 42.1.2分组码的码重和码距 52.2 汉明码编译原理 8第三章 VHDL语言与集成环境 103.1 EDA概念 103.2 Max+pluxII简介 113.3 VHDL语言 123.3.1基本介绍 123.3.2 VHDL语言设计的特点 123.3.3 VHDL语言优势 13第四章汉明码编译系统模块设计与实现 14 4.1 汉明码编译原理设计 144.2 系统模块设计 144.2.1 16位比特序列产生与分组模块 144.2.2 编码模块 164.3.3 加错模块 164.3.4 译码与分组模块 17第五章系统仿真、调试和结果分析 185.1 16位序列产生与分组模块仿真 185.1.1仿真图 185.1.2 结果分析 195.2 编码模块仿真 195.2.1仿真图 195.2.2 结果分析 195.3 加错模块 195.3.1仿真图 195.3.2 结果分析 205.4 译码与分组串行模块仿真 205.4.2 结果分析 205.5 系统仿真 205.5.1 顶层图 205.5.3 结果分析 25第六章总结 25参考文献 26附录程序: 28摘要在通信系统中,要提高信息传输的有效性,我们将信源的输出经过信源编码用较少的符号来表达信源消息,这些符号的冗余度很小,效率很高,但对噪声干扰的抵抗能力很弱。

为了提高信息传输的准确性,我们引进了差错控制技术。

而该技术采用可靠的,有效的信道编码方法来实现的。

纠错码是一种差错控制技术,目前已广泛应用于各种通信系统和计算机系统中,纠错编码主要用于数字系统的差错控制,对于保证通信、存储、媒体播放和信息转移等数字传递过程的质量有着重要意义,是通信、信息类科知识结构中不可缺少的一部分。

基于VHDL循环码编译码器(包含编码部分和纠错部分还有译码部分)

目录目录 (1)摘要 (2)1 引言 (2)1.1 课程设计目的 (4)1.2 课程设计平台 (4)2 应用工具介绍 (4)2.1 EDA 技术介绍.............................................................................. 错误!未定义书签。

2.2 VHDL语言介绍 (6)2.3 VHDL语言的特点 (6)3 设计原理 (7)3.1编码器的设计 (7)3.2译码器的设计 (9)4 设计步骤 (10)4.1 VHDL设计流程 (10)4.2 系统分析 (11)4.3 程序流程分析 (12)4.4 程序设计 (12)4.5 系统仿真 (15)4.6 结果分析 (16)5 结束语 (17)6 致谢 (18)参考文献 (19)基于VHDL语言的循环码编译码器设计摘要本课程设计设想采用专用集成电路芯片实现循环码编译码器的功能。

在本次计中,使用的系统开发平台为Quartus2Ⅱ,硬件描述语言是VHDL。

设计方案中,实现了编码,纠错,译码。

从循环的原理出发,讨论循环码编译码系统的特点。

以一个(7,4)循环码为例,使用硬件描述语言VHDL 对该系统进行了设计,能实现循环码以及一位错码的纠错译码。

依据设计方案和设计平台完成了程序编写和程序调试,通过运行程序及时序波形的仿真有效验证了设计的正确性,初步实现了设计目标。

关键词专用集成电路;VHDL;循环码编译码器;Quartus2ⅡAbstract The course is designed ASIC chip envisaged cyclic codes codec functions. In this account, the use of the system development platform for Quartus2 Ⅱ, hardware description language VHDL. Design, the realization of the coding, error correction, decoding. From the cycle of principle, to discuss the characteristics of cyclic code encoding and decoding system. A (7,4) cyclic code, for example, using hardware description language VHDL design of the system, to achieve the cyclic code and a decoding error correction codes. Design and design platform based on the completion of the programming and debugging, and timing waveforms by running the simulation program effectively validate the correctness of the design, the initial realization of the design goal.1 引言循环码是在严密的代数学理论基础上建立起来的,是线性分组码的一种。

卷积码编码原理

卷积码编码原理卷积码是一种常用的编码方式,它在通信系统中起着非常重要的作用。

卷积码编码原理是指利用卷积码对信息进行编码的基本原理,下面将对卷积码编码原理进行详细介绍。

首先,我们需要了解卷积码的结构。

卷积码是由一个或多个时变系统组成的编码器,它将输入的信息序列转换为输出的码字序列。

在卷积码编码原理中,我们需要了解卷积码的生成多项式和约束长度。

生成多项式决定了卷积码的性能,而约束长度则决定了卷积码的记忆能力。

其次,我们需要了解卷积码的编码过程。

卷积码的编码过程是通过对输入的信息序列进行卷积运算,得到输出的码字序列。

在编码过程中,卷积码的每一个输出都是由输入序列的若干个元素经过加权后得到的。

这种加权操作是通过卷积码的状态转移图来实现的,而状态转移图则是由卷积码的生成多项式和约束长度决定的。

另外,我们还需要了解卷积码的性能分析。

卷积码的性能分析是通过计算码字序列的误码率来实现的。

在卷积码编码原理中,我们需要了解卷积码的自由距离和最小距离。

自由距离是指卷积码的最大码长下的最小距离,而最小距离则是指卷积码的所有码字中最小的距离。

这两个性能参数决定了卷积码的纠错能力和译码复杂度。

最后,我们需要了解卷积码的应用。

卷积码在通信系统中有着广泛的应用,例如在无线通信、卫星通信和光纤通信中都可以看到卷积码的身影。

在这些应用中,卷积码通过提高系统的抗干扰能力和纠错能力,提高了通信系统的可靠性和稳定性。

总之,卷积码编码原理是通信系统中的重要内容,它对于理解和设计通信系统具有重要意义。

通过对卷积码的结构、编码过程、性能分析和应用进行深入了解,我们可以更好地应用卷积码技术,提高通信系统的性能和可靠性。

基于FPGA和VHDL的汉明码编解码器设计

3.1 海明码编码基本原理 ·······························································································5

目录

摘 要·············································································································· I

Abstract ·············································································································II

如果一个分组码的数据位长度为k校验位长度为r总的编码长度为kr则总的可以编码的合法码字的个数为2k总的码字个数为2n可以看出检验位的长度越长合法码字所占的比例就越小如果这些码字能够尽可能地在所有的码字中均匀分布的话合法码字之间的最小海明码距就越大编码的抗干扰能力也就越强因此设计编码方法的最重要的任务就是尽量使合法码字尽可能地均匀分差错控制编码在通信电子系统中得到广泛应用其中一类重要的差错控制编码是线性分组码线性分组码中信息位和监督位通过代数方程相联系

5.3.1 测试预期情况 ······················································································································14 5.3.2 实际硬件测试情况 ··············································································································15

(2,1,2)卷积码的译码设计

(2,1,2)卷积码的译码设计前⾔卷积码是由伊莱亚斯(Elias)于1954 年⾸先提出来的。

它充分利⽤了各组之间的相关性,本组的信息元不但决定本组的监督元,⽽且也参与决定以后若⼲组的监督元。

同时在译码过程中,不但从该时刻所收到的码组中提取译码信息,⽽且还利⽤以后若⼲时刻内所收到的码组来提取有关信息。

⽆论从理论上还是实际上均已证明其性能优于线性分组码。

近年来众多有关卷积码研究结果表明,卷积码最有希望实现⾹农信道编码定理。

但卷积码在译码理论及实际应⽤较为复杂,这些缺点限制了其进⼀步发展和应⽤。

维特⽐译码算法由维特⽐(Viterbi)1964年提出,算法实质是最⼤似然译码,但它利⽤了编码⽹格图的特殊结构,在⽹格图中选择⼀条路径,使相应的译码序列与接收到的序列之间的汉明距(即量度)最⼩的⼀种最⼤似然译码⽅法,从⽽⼤⼤降低了计算的复杂性。

⽬前,第三代移动通信系统(3G) 在我国已经开始紧锣密⿎地实施,它带来的⾼速度、⾼品质的⽆线通信服务,将使我们领略到信息技术的⽆穷魅⼒。

信道纠错编码技术作为保证信息可靠传输的技术,在3G各系统中⼴泛采⽤,并且我们现在所使⽤的第⼆代移动通信系统,如GSM、 CDMA 通信系统,还有卫星与空间通信系统⼴泛采⽤了卷积码信道编、译码技术。

本次设计将以(2,1,2)卷积码为例,通过单⽚机,实现卷积码的译码,借助RS232完成单⽚机与单⽚机、单⽚机与计算机的串⼝通信,借助7279完成键盘扫描和数码管显⽰。

第⼀章系统组成及⼯作原理本次设计的(2,1,2)卷积码的译码由89C52单⽚机为⼯具,接收来⾃另⼀单⽚机或计算机的编码信息,通过7279的键盘扫描和数码管显⽰功能可以⽅便地观察到单⽚机接收的信息和译码结果。

其系统框图如下图1-1所⽰。

MAX232芯⽚能实现EIA-RS-232C的正负电压与TTL的⾼低电平之间的转换,通过它能够⽅便实现单⽚机与单⽚机、单⽚机与计算机间的串⼝通信。

HD7279是⼀⽚具有串⾏接⼝的, 可同时驱动8位共阴极数码管的智能显⽰驱动芯⽚, 该芯⽚同时还可连接多达64键的键盘矩阵,单⽚即可独⽴完成显⽰、键盘接⼝的全部功能。

基于VHDL语言的CRC加卷积编码系统

1

CRC 加卷积编码系统原理

在 GSM 和 CDMA 系统中, 话音信息、 控制信

息和同步信息在传输过程中都使用了 CRC 码[ 1] . 其中 GSM 同步信道所使用的 CRC 循环编+ x 5 + x 6 + x 8 + x 10 . 其原理框图如图 1 所示. 最后输出的码元序列总共 35 位, 前 25 位为输 入的信息 码元, 其 余 10 位是 CRC 编码, 即从 10 个寄存器中依次输出的码元 . 卷积码在 GSM 系统中应用广泛, 例如全速率 业务信道和控制信道就采用了 ( 2, 1, 4) 卷积编码, 而 CDMA 前向和反向信道都采用了 ( 2, 1, 9) 卷积 码. 本次设计中 , 将采用( 2, 1, 4) 卷积编码 , 即输入码元数为 1, 输出码元数为 2, 编码器的寄存器数为 4. 该卷 积编码器生成多项式的原理框图如图 2 所示 , 生成多项式为 g 1 ( x ) = 1+ x + x , g 2 ( x ) = 1+ x + x + x . 图 2 中, 每个编号的方框都代表一个存放二进制码元的寄存器. 从 CRC 编码器输出的 35 位码元 , 经过 上半部分的编码以后输出 39 位, 经过下半部分的编码以后输出也是 39 位 . 选择输出 轮流从上半部分和下 半部分输出生成的码元, 因此 , 经过卷积编码输出的信息码元总共为 78 位 ( 39+ 39= 78) .

keywordscrccyclicredundancycheckconvolutionencoding责任编辑内蒙古师范大学学报自然科学汉文版荣获中国北方十佳期刊奖为了展示中国北方期刊出版业取得的成就发挥优秀期刊在出版中的示范作用进一步推动北方期刊出版事业繁荣发展由中国期刊协会和北京天津河北山西内蒙古辽宁吉林黑龙江甘肃青海宁夏等中国北方11个省自治区直辖市新闻出版局期刊协会联合主办的中国北方优秀期刊评选活动在辽宁省沈阳市举行

基于VHDL的CRC编解码设计

检错重发:在发生码元序列中加入差错控制码元,接收端利用这些码元检测到有码元时,利用反相信道通知发送端,要求发送端重发,直到正确接收为止。所谓检测到有码错,是指在一组接收码元中知道有一个或一些错码,但是不知道该错码该如何纠正。采用检错重发技术时,通信系统需要有双向信道传送重发指令。

前向纠错:前向纠错一般简称FEC(Forward Error Correction)。这时接收端利用发送端在发送码元序列中加入的差错控制码元,不但能够发现错码,还能将错码恢复其正确取值。在二进制码元的情况下,能够确定错码的位置,就相当于能够就纠正错码。

由上例可知,一种编码的最小码距直接关系到这种码的检错和纠错能力,码距实际上是由一种码组变成另一种码组必须变化的比特数。因此最小码距是信道编码的一个重要参数。在一般情况下,对于分组码有以下结论:

①为检测e个误码,要求该编码的最小码距

(2.1-1)

②为纠正t个误码,要求该编码的最小码距

VHDL的编码器和译码器的设计 (2)

1引言随着社会的发展,科学技术也在不断的进步。

计算机从先前的采用半导体技术实现的计算器到现在广泛应用的采用高集成度芯片实现的多功能计算器。

计算机电路[1]是计算机的重要组成部分,了解计算机电路的知识是促进计算机的发展的先决条件。

而编码器和译码器是计算机电路中的基本器件,对它们的了解可以为以后的进一步深化研究打下一个良好的基础。

在硬件电子电路设计领域中,VHDL语言[2]则是EDA的关键技术之一。

VHDL语言具有强大的语言结构,可用明确的代码描述复杂的控制逻辑设计,并且具有多层次的设计描述功能,支持设计库和可重复使用的元件的生成。

近十几年来,EDA技术获得飞速发展。

它以计算机为平台,根据硬件描述语言VHDL,自动地完成逻辑编辑、化简分割、综合及优化,布局布线,仿真直至对特定目标芯片的适配编译,逻辑映射和编程下载等工作。

在本设计主要介绍的是一个基于超高速硬件描述语言VHDL对计算机电路中编码器和译码器进行编程实现。

本设计主要介绍的是一个基于超高速硬件描述语言VHDL对计算机电路中编码器和译码器进行编程实现。

1.1 课程设计的目的本次设计的目的就是通过实践掌握计算机组成原理的分析方法和设计方法,了解EDA技术并掌握VHDL硬件描述语言的设计方法和思想。

以计算机组成原理为指导,通过学习的VHDL语言结合电子电路的设计知识理论联系实际,掌握所学的课程知识和基本单元电路的综合设计应用。

通过对基于VHDL的编码器和译码器的设计,巩固和综合运用所学知识,提高IC设计能力,提高分析、解决计算机技术实际问题的独立工作能力。

1.2 课程设计的基本内容根据计算机组成原理[3]中组合逻辑电路设计的原理,利用VHDL设计计算机电路中编码器和译码器的各个模块,并使用EDA 工具对各模块进行仿真验证和分析。

(1)熟悉编码器、译码器的工作原理,合理利用各种软硬件资源。

本设计编码器由八-三优先编码器作为实例代表,而译码器则包含三-八译码器和二-四译码器两个实例模块组成。

卷积码编码器的设计1汇总

湖南文理学院课程设计报告学生姓名: 指导教师:完成时间:2014-11-18报告成绩:课程名称: 通信系统课程设计 专业班级:通信工程11102班09朱涛 侯清莲、设计要求 二、设计作用与目的 三、所用设备及软件 四、卷积码编码的概念五、EDA 设计方法及工具软件QUARTUB7.1 VHDL 设计的优点与设计方法八、心得体会 九、参考文献目录4.1卷积码的编码描述方法4.3 4.44.2 卷积编码 卷积码的树状图 卷积码的网格图六、 改变卷积编码器的参数仿真以及结论6.1 不同回溯长度对卷积编码器性能的影响 6.2 不同码率对卷积编码器误码性能的影响 6.3不同约束长度对卷积编码器的误码性能影响七、 卷积码编码器的VHDL 设计与仿真7.2卷积码编码器的VHDL 实现10 10 11卷积编码器的设计三、所用设备及软件(1) QUARTUS ⑵PC 机四、卷积码编码的概念4.1卷积码的编码描述方法编码描述方法有5种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述法和网格图描述法。

卷积码的纠错能力随着N 的增加而增大,而差错率随着 N 的增加而指数下降。

在编码器复杂性相同的情况下,卷积码的性能优于分组码。

分组码有严格 的代数结构,但卷积码至今尚未找到如此严密的数学手段。

分组码的译码算法可以由其代 数特性得到。

卷积码虽然可以采用适用于分组码的门限译码(即大数逻辑译码),但性能 不如维特比译码和序列译码[2]。

以二兀码为例,输入信息序列为 u = ( U 0,U 1,…),其多项式表示为u(x) = U 0+U 1X +…+…。

编码器的连接可用多项式表示为 g 1,1)(x) = 1+X+X 2和g (1,2)(x) = 1+x 2,称为码的子生 成多项式。

它们的系数矢量g (1,1)=(111)和g (1,2)=(101)称作码的子生成元。

以子生成多项式 为阵元构成的多项式矩阵 G(x) =[ g (1,1)(x), g (1,2)(x)],称为码的生成多项式矩阵。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

专业课程设计报告题目:利用VHDL实现(2,1,2)卷积码编码姓名:专业:通信工程班级学号:同组人:指导教师:南昌航空大学信息工程学院20 17 年6 月27 日专业课程设计任务书2016-2017学年第 2 学期第 17 周- 19 周摘要在现代数字通信中,为降低数据传输的误码率,提高通信质量及其可靠性,常在通信中采用纠错编码技术。

其中卷积码就是一种具有较强纠错能力的纠错码。

由于Vitebrbi译码算法比较容易实现,卷积码得到了广泛应用。

本课题简明地介绍了用EDA技术实现卷积码编码器的实现。

卷积码纠错性能常常优于分组码,是一种性能优越的信道编码。

由于码字之间的相关性,其编码器要利用移位寄存器来存储状态。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

卷积码作为通信系统中重要的编码方式,以其良好的编码性能,合理的译码方式,被广泛应用。

本文在阐述卷积码编码器基本工作原理的基础上,给出了(2,1,2)卷积编码器的VHDL设计,在QuartusⅡ环境下进行了波形功能仿真,并下载到EP1C6T144C8N芯片上进行验证,最终实现输入四位序列,编码输出八位通过指示灯显示。

关键词:卷积码QuartusⅡEP1C6T144C8N目录:摘要 (4)目录: (5)第一章系统设计要求 (6)1.1系统设计要求 (6)第二章系统组成与工作原理 (6)2.1系统组成 (6)2.2编码器设计原理 (6)2.2.1结构图法描述编码器 (7)2.2.2(2,1,2)卷积码的状态转移图 (8)第三章编码器设计方案与对比选择 (9)第四章 VHDL语言实现及仿真调试 (10)4.1编码器电路设计 (10)4.2VHDL描述编码器 (11)4.2调试 (12)第五章 FPGA编程下载 (15)第六章实验心得 (16)参考文献 (17)第一章系统设计要求1.1系统设计要求1.设计一个(2,1,2)卷积码编码器。

2.在FPGA上用VHDL硬件描述语言实现上述编码器和译码器。

3. 通在试验箱上过拨码开关输入信息序列,观察编码输出(即指示灯的亮灭)第二章系统组成与工作原理2.1系统组成2.2编码器设计原理卷积码也是分组码,但它的监督码元不仅与本组的信息码(k位)有关,而且还与前面若干组(m组)的信息码元有关。

用(n,k,m)表示。

卷积编码的原理框:图2-1 图图图图图图图卷积编码的编码约束长度定义为:串行输入比特通过编码其所需的移位次数,它表示编码过程中相互约束的分支码数,所以具有m级移位寄存器的编码器得约束长度为m十1,有时也说(m十1)n为卷积编码的编码约束长度。

与分组编码一样,卷积编码的编码效率也定义为R=k/n,与分组码具有固定码长n不同,卷积码没有,我们可通过周期性地截断来获得分组长度。

为了达到清空编码移位寄存器数据bit的目的,需要在输入数据序列末尾附加若干0bit。

由于附加的0不包含任何信息,因而,有效编码效率降至k/n以下,如果截断周期取值较大,则有效编码效率会逼近k/n。

2.2.1结构图法描述编码器卷积码编码器主要由移位寄存器和模2加法器组成,(2,1,2)卷积码编码器结构图如下:图2-2-1 图2,1,2图图图图图图图图图图2.2.2(2,1,2)卷积码的状态转移图该状态图描述了编码器每输入一个信息元时,编码器各可能状态以及伴随状态的转移所产生的分支码字。

图2-2-2 (2,1,2)卷积编码器状态转移图图中的小框表示寄存器的状态,连接小框的箭头表示状态转移的方向,两线旁的数字表示:输出分支码字/输入信息比特。

状态图简明的表示了在某一时刻编码器的输入比特和输出分支码字的关系。

2.2.3(2,1,2)卷积码的生成多项式●卷积码编码器第i 条支路的生成多项式g ()i (D)= ()()()2()012...i i i i k k g g D g D g D ++++,对于(2,1,2)卷积码其生成多项式为:g(1)(D)=1+D+2D , g (2)(D)=1+2D ,信息序列a=(0121,,,...,N a a a a -)也可表示为a(D)= 210121...N N a a D a D a D --++++,相应的第i 条路径的输出为()()()()()i i v D g D a D =,输出序列可根据v(D)= g (1)(D)a(D)与g(2)(D) a(D) 交织求得。

● 该(2,1,2)卷积码,一位输入有两位输出,两位都是检验位,信息位被隐藏。

生成多项式为 g1=x ²+x+1 g2=x ²+1生成矩阵为G=[11100101100110110000000111000011] 生成矩阵每一行都是码字,即分别是1000,0100,0010,0001四种输入的编码输出,输入其他任意四位序列,其编码输出可以由对应行模2加得到。

以输入序列1101为例,其编码过程如下:输入:1101=1000⊕0100⊕0001输出: 11101000=11101100⊕00111011⊕00000011第三章 编码器设计方案与对比选择 根据前面对卷积码的描述,实现(2,1,2)编码器主要采用以下两种方案●方案一:(2,1,2)卷积码总共只有四种状态,对其采用二进制编码00,01,10,11,任意时刻输入0/1,其输出都在四种状态间跳转。

利用编码后的状态作为输出显示。

●方案二:用(2,1,2)卷积码两个生成多项式分别与输入信号卷积得到两位编码输出。

其间要设置寄存器的状态,并在输入时刻实现寄存器的移位功能。

最终通过模2加得到两位输出再通过中间存储输出最终序列。

实验箱上通过一位拨码开关控制输入,两个指示灯显示编码输出的跳换。

●对比选择两种方案的VHDL语言实现都较为简单。

都需要最初控制复位信号对寄存器清零。

但是最终实现下来,发现方案一较为局限。

虽然仿真结果成功,输入任意随机序列,可以达到编码效果,但是在实验箱上控制发现,因其只有一个输入,所以只用通过一位拨码开关实现输入,而实验箱上时钟频率过高,最后分频虽然能得到正确的编码输出,但输入太局限只能是一串1或0,最终显示灯停在10或者00状态,想要实现输入任意序列对时钟频率的要求过高,短时间难以实现。

而方案二通过改进,实现起来简单,可以直接通过四个拨码开关控制输入,显示灯直接显示8位编码后的输出。

所以综合优缺点,最终以方案二进行设计。

第四章VHDL语言实现及仿真调试4.1编码器电路设计(2,1,2)卷积码编码器模型图4.2VHDL描述编码器library ieee;use ieee.std_logic_arith.all;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity juanji1 isport(clk,rst:in std_logic;d:in std_logic_vector(3 downto 0);s:out std_logic_vector(9 downto 0));end entity; --编码器输入输出端口architecture behave of juanji1 issignal temp:std_logic_vector(9 downto 0);signal c1:std_logic_vector(4 downto 0);signal c2:std_logic_vector(4 downto 0); --中间变量,存储输出signal m:std_logic_vector(2 downto 0); --寄存器状态存储signal n:integer range 0 to 7;--signal rst1:std_logic; --只截取一次编码输出,截断后面的编码--signal cnt:std_logic_vector(3 downto 0);begin--process(rst,clk)--begin--if(clk'event and clk='1') then--if(cnt(3)='0') then--rst1<='0';--cnt<=cnt+1;--else--rst1<='1';--end if;--end if;--elsif(rst='1') then--rst1<='1';--end if;--end process; --控制复位信号,截断后续编码process(rst,clk)beginif(rst='1') thenm<="000";n<=0; --寄存器初始清零elseif (clk'event and clk='1') thenm(0)<=m(1);m(1)<=m(2);m(2)<=d(n); --时钟上升沿输入一位信息temp(2*n)<=c1(n);temp(2*n+1)<=c2(n); --暂存输出n<=n+1;end if;end if;end process;c1(n)<=m(0) xor m(1) xor m(2);c2(n)<=m(0) xor m(2); --编码输出逻辑描述s<=temp;end behave;4.2调试c1(n)<=m(0) xor m(1) xor m(2);c2(n)<=m(0) xor m(2);这两句是对编码输出的逻辑描述,最初放在进程中,发现系统报错:后查书发现,这两句属于简单信号赋值语句,属于并行语句,要放在结构体中,进程中是顺序语句,所以出错。

修改后虽然编译成功,也能仿真,但是8位输出中,前两位始终是0,而第四个信息位并没有实现编码,这是因为结构体中这两句复制信号并行执行,所以最开始就会把最低两位赋值,始终占据最低两位。

要想最后一位也编码,必须扩大输出,最终将8位输出扩大为10 位后,成功得到编码。

仿真如下:由上个仿真结果清楚地看到,虽然得到正确编码,但因为复位信号的无效,所以一直在输入状态,编码并不止一次,而由于卷积码编码是利用码字之间的相关性,后续编码实在是不好分析,最终通过控制复位信号实现截断,使之只产生一次编码,最终仿真如下:图仿真实现了输入1101,输出11010100。

●后续编码分析(不截断)为正确分析后续编码,将中间变量n添加进来。

temp(n)是个一维数组型变量,用来暂存输出。

n是个整形变量范围是0-4;quartus中自动用三位二进制数表示,三位二进制最大可以表示8个数,按照我们设定的temp的值,n只能取其中的五个数。