基于matlab的2-3卷积码编码译码设计与仿真

基于Matlab的卷积码译码器的设计与仿真

基于Matlab的卷积码译码器的设计与仿真作者:曹亚陆来源:《硅谷》2011年第15期摘要:主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通过Matlab软件进行设计与仿真,并进行误码率分析。

系统开发平台为Windows Vista Ultimate,程序设计与仿真均采用Matlab R2007a(7.4),最后仿真详单与理论分析一致。

关键词:卷积码译码器;Matlab;Simulink;设计与仿真中图分类号:TP314 文献标识码:A 文章编号:1671-7597(2011)0810049-011 概述设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通过Matlab软件进行设计与仿真。

卷积码的译码有两种方法——软判决和硬判决,此课程设计采用硬判决的维特比译码。

1.1 设计目的。

卷积码是一种向前纠错控制编码。

它将连续的信息比特序列映射为连续的编码器输出符号。

这种映射是高度结构化的,使得卷积码的译码方法与分组码译码所采用的方法完全不同。

可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。

对于某个特定的应用,采用分组编码还是采用卷积编码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术[1]。

本设计便是通过Matlab设计一个硬判决维特比译码输出的完整电路,并进行误码率分析。

1.2 设计的原理。

卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。

卷积编码的最佳译码准则为:在给定已知编码结构、信道特性和接收序列的情况下,译码器将把与已经发送的序列最相似的序列作为传送的码字序列的估值。

对于二进制对称信道,最相似传送序列就是在汉明距离上与接收序列最近的序列。

2 维特比译码原理采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。

如果发送L组信息比特,那么对于(n,k)卷积码来说,可能发送的序列有2kL个,计算机或译码器需存储这些序列并进行比较,以找到码距最小的那个序列。

基于MATLAB的卷积码的分析与应用

基于MATLAB的卷积码的分析与应用毕业设计(论文)任务书基于MATLAB的卷积码的分析与应用摘要随着现代通信的发展,特别是在未来4G通信网络中,高速信息传输和高可靠性传输成为信息传输的两个主要方面,而可靠性尤其重要。

因为信道状况的恶劣,信号不可避免会受到干扰而出错。

为实现可靠性通信,主要有两种途径:一种是增加发送信号的功率,提高接收端的信号噪声比;另一种是采用编码的方法对信道差错进行控制。

前者常常受条件限制,不是所有情况都能采用。

因此差错控制编码得到了广泛应用。

介绍了多种信道编码方式,着重介绍了卷积码的编码方法和解码方式。

介绍了MATLAB的使用方法、编程方法、语句、变量、函数、矩阵等。

介绍了TD-SCDMA通信系统和该系统下的卷积码,搭建了系统通信模型。

编写卷积码的编码和解码程序。

用MATLAB仿真软件对TD-SCDMA系统的卷积码编解码进行仿真。

对其纠正错码性能进行验证,并且对误码率进行仿真和分析。

卷积码的编码解码方式有很多,重点仿真Viterbi算法。

Viterbi算法就是利用卷积码编码器的格图来计算路径度量,选择从起始时刻到终止时刻的惟一幸存路径作为最大似然路径。

沿着最大似然路径回溯到开始时刻,所走过的路径对应的编码输出就是最大似然译码输出序列。

它是一种最大似然译码方法,当编码约束长度不大、或者误码率要求不是很高的情况下,Viterbi译码器设备比较简单,计算速度快,因而Viterbi译码器被广泛应用于各种领域。

关键词:卷积码;信道编码;TD-SCDMA;MATLAB目录毕业设计(论文)任务书 (I)摘要 (II)Abstract......................................................................................... 错误!未定义书签。

第1章绪论 . (1)1.1课题研究的背景和来源 (1)1.2主要内容 (2)第2章相关理论介绍 (3)2.1信道编码 (3)2.1.1 信道编码的分类 (3)2.1.2 编码效率 (3)2.2线性分组码 (3)2.3循环码 (5)2.4卷积码 (6)2.4.1 卷积码简介 (7)2.4.2 卷积码的编码 (7)2.4.3 卷积码的解码 (13)第3章MATLAB应用 (21)3.1数和算术的表示方法 (21)3.2向量与矩阵运算 (21)3.2.1 通过语句和函数产生 (21)3.2.2 矩阵操作 (22)3.3矩阵的基本运算 (22)3.3.1 矩阵乘法 (22)3.3.2 矩阵除法 (23)3.4MATLAB编程 (23)3.4.1 关系运算 (23)3.4.2 控制流 (25)第4章卷积码的设计与仿真 (27)4.1TD-SCDMA系统 (27)4.1.1 系统简介 (27)4.1.2 仿真通信系统模型 (27)4.2卷积编码设计 (28)4.3编解码程序实现 (29)4.3.1 卷积码编解码设计 (29)4.3.2 卷积码编解码程序设计 (32)4.4卷积码实现 (34)4.4.1 (2,1)卷积码的仿真研究 (34)4.4.2 (3,1)卷积码的仿真研究 (36)4.5卷积码误码率 (38)第5章结论 (41)5.1总结 (41)5.2展望 (41)参考文献 (43)致谢 (45)第1章绪论1.1课题研究的背景和来源纠错编码己有五十几年历史,早在1948年,香农(Shannon)在他的开创性论文“通信的数学理论”中,首次阐明了在有扰信道中实现可靠通信的方法,提出了著名的有扰信道编码定理,奠定了纠错码的基石。

基于Matlab的卷积码编译器设计

1本科生毕业论文(设计)题目:基于Matlab 的卷积码编译器设计仿真专业代码: 080603作者姓名:张倍红学号: **********单位:物理科学与信息工程学院指导教师:***2010年 5 月 20日目录引言 (1)1.系统仿真 (1)1.1系统仿真的定义 (1)1.2仿真模型与仿真研究 (1)2.MATLAB仿真 (3)3.差错控制编码 (4)3.1差错控制编码 (4)3.1.1 概述 (4)3.1.2 差错控制编码方法 (4)4.卷积码编译器设计仿真 (5)4.1卷积码 (5)4.2卷积码的编码 (6)4.3卷积码的译码 (8)4.4相关参数 (11)4.5程序设计 (11)4.5.1 卷积码编码函数 (11)4.5.2 维特比译码函数 (12)4.6卷积码的性能分析和仿真测试 (13)4.6.1 理论计算 (13)4.6.2 仿真结果与理论 (14)结束语 (17)参考文献 (19)致谢 (20)摘要本文通过对卷积码的研究,用Matlab实现了卷积码的冲击响应编码和Viterbi译码,通过一系列的仿真实验进一步证明了卷积码的特性,从而说明卷积码是一种非常有前途的、能达到信道编码定理所提出的码类。

最后通过 Matlab仿真,对卷积码的性能进行了理论分析和实验仿真。

关键词:卷积码;Viterbi;Matlab;误比特率AbstractIt makes a deeply analytical study about convolution code in this article and it makes a convolution impact response coding & Viterbi decoding also, the characteristics of convolution code was fully proved by a series of simulated experiment, it shows that convolution code is a perfect code style which is promising & fitting. In the end, the performance of convolution code is analyzed and simulated based on Matlab Keywords: convolution code; Viterbi; Matlab; bit error rate基于Matlab的卷积码编译器设计仿真引言由于数字信号在传输过程中受到干扰的影响。

卷积码的编解码仿真与研究

卷积码的编解码仿真与研究摘要卷积码是一种性能优越的信道编码。

它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

本文简明地介绍了卷积码的编码原理和译码原理。

并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。

最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。

经过仿真和实测,并对测试结果作了分析。

得出了以下三个结论:(1)当改变卷积码的码率时,系统的误码性能也将随之发生变化。

(2)对于码率一定的卷积码,当约束长度N 发生变化时,系统的误码性能也会随之发生变化。

(3)回溯长度也会不同程度上地影响误码性能。

关键词:卷积码;码率;约束长度;回溯长度Simulation and Research on Encoding and Decoding ofConvolution CodeAbstractConvolution code has a superior performance of the channel code. It is easy to coding and decoding. And it has a strong ability to correct errors. As correcting coding theory has a long development, the practice of convolution code is more and more extensive. In this thesis, the principle of convolution coding and decoding is introduced simply firstly. Then the whole simulation module process of encoding, decoding and the Error Rate Calculation is completed in this design. Finally, in order to understand their performances of error rate, many changes in parameters of convolution code are calculated in the simulation process. After simulation and measure, an analysis of test results is presented. The following three conclusions are draw:(1) When the rate of convolution Code changes, BER performance of the system will change.(2) For a certain rate of convolution code, when there is a change in the constraint length of N, BER performance of the system will change.(3) Retrospective length will affect BER.Key words: convolution code; rate; constraint length; retrospective length;目录论文总页数:21页1 引言 (1)1.1 课题背景 (1)1.2 国内外研究现状 (1)1.3 本课题的意义 (1)1.4 本课题的研究方法 (1)2 卷积码的基本概念 (2)2.1 信道 (2)2.2 纠错编码 (2)2.3 卷积码的基本概念 (2)2.4 卷积码编码的概念 (2)2.4.1 卷积编码 (2)2.4.2 卷积码的树状图 (3)2.4.3 卷积码的网格图 (4)2.4.4 卷积码的解析表示 (5)3 卷积码的译码 (6)3.1 卷积码译码的概述 (6)3.2 卷积码的最大似然译码 (6)3.3 VITEBI 译码的关键步骤 (7)3.3.1 输入与同步单元 (7)3.3.2 支路量度计算 (7)3.3.3 路径量度的存储与更新 (7)3.3.4 信息序列的存储与更新 (8)3.3.5 判决与输出单元 (8)4 结论 (9)4.1 卷积码的仿真 (9)4.1.1 SIMULINK仿真模块的参数设置以及重要参数的意义 (9)4.2 改变卷积码的参数仿真以及结论 (12)4.2.1 不同回溯长度对卷积码性能的影响 (12)4.2.2 不同码率对卷积码误码性能的响 (14)4.2.3 不同约束长度对卷积码的误码性能影响 (15)结论 (17)参考文献 (18)致谢..................................................... 错误!未定义书签。

213卷积码编码和译码

No.15 (2,1,3)卷积码的编码及译码摘要:本报告对于 (2,1,3)卷积码原理部分的论述主要参照啜刚教材和课件,编程仿真部分绝对原创,所有的程序都是在Codeblocks 8.02环境下用C语言编写的,编译运行都正常。

完成了卷积码的编码程序,译码程序,因为对于短于 3 组的卷积码,即2 bit 或4 bit 纠错是没有意义的,所以对正确的短序列直接译码,对长序列纠错后译码,都能得到正确的译码结果。

含仿真结果和程序源代码。

如果您不使用Codeblocks 运行程序,则可能不支持中文输出显示,但是所有的数码输出都是正确的。

一、卷积码编码原理卷积码编码器对输入的数据流每次1bit或k bit进行编码,输出n bit编码符号。

但是输出的分支码字的每个码元不仅于此时可输入的k个嘻嘻有关,业余前m个连续式可输入的信息有关,因此编码器应包含m级寄存器以记录这些信息。

k通常卷积码表示为(n,k,m).编码率r —n当k=1时,卷积码编码器的结构包括一个由m个串接的寄存器构成的移位寄存器(成为m级移位寄存器、n个连接到指定寄存器的模二加法器以及把模二加法器的输出转化为穿行的转换开关。

本报告所讲的(2,1,3)卷积码是最简单的卷积码。

就是n 2,k 1,m 3的卷积码。

每次输入1 bit输入信息,经过3级移位寄存器,2个连接到指定寄存器的模二加法器,并把加法器输出转化为串行输出。

EncoderOuTi>iit编码器如题所示。

二、卷积码编码器程序仿真C语言编写的仿真程序。

为了简单起见,这里仅仅提供数组长度30 bit的仿真程序,当然如果需要可以修改数组大小。

为了更精练的实现算法,程序输入模块没有提供非法字符处理过程,如果需要也可以增加相应的功能。

进入程序后,先提示输入数据的长度,请用户输入int (整型数)程序默认用户输入的数据小于30,然后提示输入01数码,读入数码存储与input数组中,然后运算输出卷积码。

基于Matlab编译码器的仿真与设计

摘要摘要本课程设计主要解决信源编码和信道编码中的卷积码的数字调制,信源输出的模拟信号要转换成数字信号,就需要对信源信道进行编码译码操作,并通过Simulink软件进行设计与仿真,进行误码率分析。

卷积码是一种性能优越的信道编码。

它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

本文简明地介绍了卷积码的编码原理和译码原理。

并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。

最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。

经过仿真和实测,并对测试结果作了分析。

得出了以下三个结论:(1)当改变卷积码的码率时,系统的误码性能也将随之发生变化。

(2)对于码率一定的卷积码,当约束长度N 发生变化时,系统的误码性能也会随之发生变化。

(3)回溯长度也会不同程度上地影响误码性能。

关键词:编译码器;simulink;设计与仿真卷积码;码率ABSTRACTABSTRACTThis course is designed to solve source coding and channel coding convolutional codes in the digital modulation, the source output analog signals into digital signals to be converted to the need for the source and channel coding and decoding operations, and through the Simulink software design and simulation, and the bit error rate analysis. Convolutional code is a superior performance of channel coding. Its encoder and decoder are relatively easy to implement, and it has a strong error correction capability. Error-correcting coding theory research with the deepening of the practical application of convolutional codes more widely. This concise introduction to the principles of convolutional coding and decoding principles. SIMULINK module in the design, completed the coding and decoding convolutional code and bit error statistics of the whole process simulation module. Finally, changes in the simulation process of convolutional codes, respectively, to deepen our understanding of the important parameters of these parameters on convolutional codes convolutional codes error performance. The simulation and measurement, and test results are analyzed. Reached the following three conclusions:(1) When the change rate convolutional code, the system error performance will subsequently change.(2) For a certain rate convolutional codes, when the constraint length N changes, the system BER performance also will be changed.(3) back length will be affected to varying degrees, error performance. Keywords: codec; simulink;design and simulation of convolutional code目录第1章引言 (1)1.1 课题背景 (1)1.2 国内外研究现状 (1)1.3 本课题的意义 (1)1.4 本课题的研究方法 (2)第2章 MATLAB组件介绍及通信系统概述 (3)2.1 MATLAB与通信仿真的发展现状及应用 (3)2.2 通信系统概述与组成 (3)2.3 通信仿真 (4)2.4 Simulink仿真及工作原理 (6)第3章信源编码 (8)3.1 A律μ律编码特性 (8)3.1.1 A律编码 (8)3.1.2 μ律编码 (8)3.1.3 A律13折线 (9)3.2 A律、μ律的特性比较 (11)第4章信道编码及译码 (15)4.1 卷积码的概念介绍 (15)4.2 卷积码的编码过程介绍 (15)4.3 卷积码译码过程的概述 (16)4.4 卷积码的最大似然译码 (19)4.5 输入与同步单元 (21)第5章卷积码的仿真 (22)5.1 Simulink仿真模块的参数设置以及重要参数的意义 (22)5.2 简化维特比译码器的仿真 (26)第6章卷积码译码器的误码率分析 (28)6.1信噪比与误码率的关系 (28)6.2.不同回溯长度对卷积码性能的影响 (29)6.3 不同码率对卷积码误码性能的响 (31)6.4 不同约束长度对卷积码的误码性能影响 (32)第7章结论 (35)参考文献 (36)致谢 (37)第1章引言第1章引言1.1 课题背景随着现代通信的发展,高速信息传输和高可靠性传输成为信息传输的两个主要方面,而可靠性尤其重要。

卷积编码与解码的MATLAB实现及性能分析

积编码与解码的MATLAB实现及性能分析摘要本课程设计主要解决通信系统中卷积编码与解码技术在Matlab中实现以及对其性能进行分析。

用贝努利二进制序列产生器作为信号源,产生基带信号,对其中的卷积进行编码,调制解调,然后采用Viterbi译码输出,最后计算误码率,对其性能进行分析。

关键词卷积码;卷积编码器;Viterbi译码器;BSK调制与解调;约束长度。

目录1引言 (4)1.1课程设计的目的 (4)1.2 课程设计的基本任务和要求 (4)1.2.1本次课程设计的基本任务 (4)1.2.2课程设计中的要求 (5)1.3设计平台 (5)2设计原理 (5)2.1卷积码的基本概念 (5)2.2卷积码的编码 (5)2.2.1卷积编码 (5)2.2.2卷积码的树状图 (6)2.2.3卷积码的网格图 (7)2.2.4卷积码的状态图 (8)2.3卷积码的解码 (8)3卷积码的仿真与性能分析 (9)3.1 卷积码的仿真 (9)3.1.1卷积码的设计框图 (9)3.1.2Simulink仿真模块的参数设置 (9)3.2 卷积码的波形输出 (15)3.2.1输入信号波形 (15)3.2.2输入信号与解码输出波形 (16)3.3卷积码的性能分析 (17)4出现的问题及解决方法 (19)5 结束语 (19)6参考文献 (20)1 引言本课程设计主要解决基于Matlab的Simulink下的模块对卷积编码与解码进行仿。

通过仿真可以更清楚的认识到卷积码的编码与解码的各个环节,并对仿真结果进行分析。

得出Viterbi译码的误码率性能和约束长度的关系。

1.1课程设计目的卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码[4]。

卷积码是一种向前纠错控制编码。

它将连续的信息比特序列映射为连续的编码器输出符号。

这种映射是高度结构化的,使得卷积码的译码方法与分组码译码所采用的方法完全不同。

可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。

基于MATLAB的CRC编码与译码的设计与仿真

*******************实践教学*******************兰州理工大学计算机与通信学院2012年春季学期《计算机通信与网络》课程设计题目:差错控制编码的编译码设计与仿真专业班级:09级通信工程(4)班姓名:杜春娟学号:09250436指导教师:彭铎成绩:通信是信息远距离的传送,是人类生产和生活的主要支撑。

通信的目的是要把信息及时可靠地传送给对方,在数据通信过程中,衰损、失真、和噪声会使通信线路上的信号发生错误。

差错控制可以减少错误、提高通信质量,可以改善传输信道的电气特性,使误码率达到要求。

CRC(Cyclical Redundancy Checking)循环冗余校验码是一种重要的线性分组码,通过多项式除法检测错误,是在数据通信和数据检测中广泛应用的检错校验的循环码。

本设计研究了CRC循环冗余校验码的原理,以及利用C语言对其进行了编程和编译仿真,实现了CRC循环冗余校验码的编码及校验,在接收端收到通过校验的码,从而确定传输过程是否出错,得到的结论和理论上是一致的。

关键词:检错码;CRC循环冗余校验码;C语言随着科学技术的进步, 人们对信息传递的要求逐渐提高。

但在通信系统中, 可靠性与有效性是对矛盾, 要求有效性提高, 必然使每个码元所占的时间缩短, 从而受干扰和产生错误的可能性增大, 可靠性降低了; 要提高信息的可靠性,又使信息速率变慢有效性降低。

在实际信道上传输数字信号时,由于信道传输特性不理想及加性噪声的影响,所收到的数字信号不可避免的会发生错误。

为了加强通信系统的可靠性,除了合理设计基带信号,选择调制、解调方式,采用频域均衡、时域均衡之外,还需要采用信道编码,即差错控制编码,使误码率进一步降低,来满足指标要求。

循环冗余校验码CRC(Cyclical Redundancy Checking)是目前通信系统中最常用的一种差错控制编码。

循环冗余校验码是一种高效率且可靠的方法, 由线性分组码分支而来的, 是一种通过多项式除法检测错误的很不寻常而又巧妙的方法, 一方面它有很强的检测能力, 二是它的编码器电路及错误检测器电路都很容易实现, 它的优点使它在通信系统中得到了广泛的应用。

Matlab的卷积码译码器的设计与仿真

Matlab的卷积码译码器的设计与仿真540802 112008111郭林《基于Matlab的卷积码译码器的设计与仿真》第1页共17页Matlab**本课程设计主要解决对一个输入信号进行卷积码编码,以及维特比(Viterbi)译码输出,并通过Matlab软件进行设计与仿真,并进行误码率分析。

程序设计与仿真均采用Matlab R2007a(7.4),最后仿真详单与理论分析一致。

卷积码编码器;卷积码译码器;Matlab;设计与仿真1本课程设计主要解决对一个信号进行信道编解码,采用卷积码编码,维特比(Viterbi)译码输出,并通过Matlab软件进行设计与仿真。

卷积码的译码有两种方法——软判决和硬判决,此课程设计采用硬判决的维特比译码。

1.1卷积码是一种向前纠错控制编码。

它将连续的信息比特序列映射为连续的编码器输出符号。

这种映射是高度结构化的,使得卷积码的译码方法与分组码译码所采用的方法完全不同。

可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。

对于某个特定的应用,采用分组编码还是采用卷积编码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术。

本课程设计便是通过Matlab,构造了一个卷积码编码后,通过产生加性高斯白噪声的信道,再进行译码的过程,译码后计算误码率,并进行分析。

郭林《基于Matlab的卷积码译码器的设计与仿真》第2页共17页 1.2 2卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。

卷积编码的最佳译码准则为:在给定已知编码结构、信道特性和接收序列的情况下,译码器将把与已经发送的序列最相似的序列作为传送的码字序列的估值。

对于二进制对称信道,最相似传送序列就是在汉明距离上与接收序列最近的序列。

卷积码的译码方法有两大类:一类是大数逻辑译码,又称门限译码(硬判决,编者注);另一种是概率译码(软判决,编者注),概率译码又分为维特比译码和序列译码两种。

卷积码的编译码原理和仿真 论文

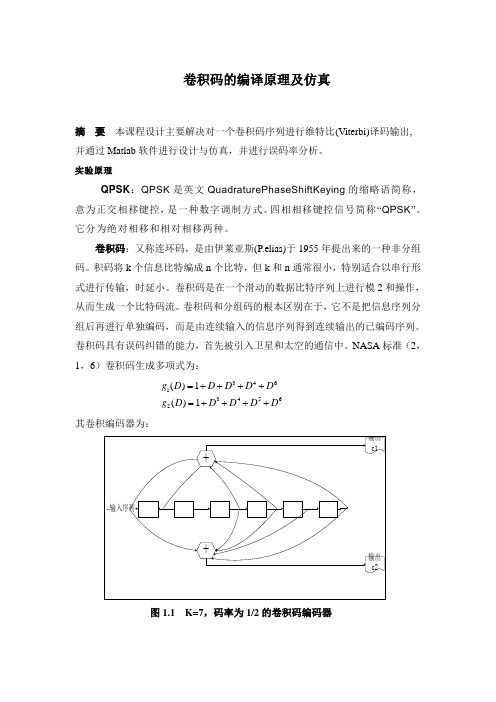

卷积码的编译原理及仿真摘 要 本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通过Matlab 软件进行设计与仿真,并进行误码率分析。

实验原理QPSK :QPSK 是英文QuadraturePhaseShiftKeying 的缩略语简称,意为正交相移键控,是一种数字调制方式。

四相相移键控信号简称“QPSK ”。

它分为绝对相移和相对相移两种。

卷积码:又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。

积码将k 个信息比特编成n 个比特,但k 和n 通常很小,特别适合以串行形式进行传输,时延小。

卷积码是在一个滑动的数据比特序列上进行模2和操作,从而生成一个比特码流。

卷积码和分组码的根本区别在于,它不是把信息序列分组后再进行单独编码,而是由连续输入的信息序列得到连续输出的已编码序列。

卷积码具有误码纠错的能力,首先被引入卫星和太空的通信中。

NASA 标准(2,1,6)卷积码生成多项式为:346134562()1()1g D D D D Dg D D D D D=++++=++++ 其卷积编码器为:输入序列++输出c1输出c2图1.1 K=7,码率为1/2的卷积码编码器维特比译码:采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。

如果接收到L 组信息比特,每个符号包括v 个比特。

接收到的Lv 比特序列与2L 条路径进行比较,汉明距离最近的那一条路径被选择为最有可能被传输的路劲。

当L 较大时,使得译码器难以实现。

维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。

它并不是在网格图上一次比较所有可能的2kL 条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。

下面以图2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。

卷积码实验报告

现代编码理论基于MATLAB的卷积码编码及译码仿真姓姓名名:闫嘉川学学号号:1433170所在院系:电子与信息工程学院实验名称:基于MAATLAB的卷积码编码及译码仿真实验目的:卷积码是一种性能优越的信道编码。

它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

本实验简明地介绍了卷积码的编码原理和Viterbi译码原理。

并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。

最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。

经过仿真和实测,并对测试结果作了分析。

实验原理:1、卷积码编码原理卷积码是一种性能优越的信道编码,它的编码器和解码器都比较易于实现,同时还具有较强的纠错能力,这使得它的使用越来越广泛。

卷积码一般表示为(n,k,K)的形式,即将 k个信息比特编码为 n 个比特的码组,K 为编码约束长度,说明编码过程中相互约束的码段个数。

卷积码编码后的 n 各码元不经与当前组的 k 个信息比特有关,还与前 K-1 个输入组的信息比特有关。

编码过程中相互关联的码元有 K*n 个。

R=k/n 是编码效率。

编码效率和约束长度是衡量卷积码的两个重要参数。

典型的卷积码一般选 n,k 较小,K 值可取较大(>10),但以获得简单而高性能的卷积码。

卷积码的编码描述方式有很多种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述,树图描述,网格图描述等。

2、卷积码Viterbi译码原理卷积码概率译码的基本思路是:以接收码流为基础,逐个计算它与其他所有可能出现的、连续的网格图路径的距离,选出其中可能性最大的一条作为译码估值输出。

概率最大在大多数场合可解释为距离最小,这种最小距离译码体现的正是最大似然的准则。

卷积码的最大似然译码与分组码的最大似然译码在原理上是一样的,但实现方法上略有不同。

基于MATLAB的CRC编码与译码的设计与仿真

摘要通信是信息远距离的传送,是人类生产和生活的主要支撑。

通信的目的是要把信息及时可靠地传送给对方,在数据通信过程中,衰损、失真、和噪声会使通信线路上的信号发生错误。

差错控制可以减少错误、提高通信质量,可以改善传输信道的电气特性,使误码率达到要求。

CRC(Cyclical Redundancy Checking)循环冗余校验码是一种重要的线性分组码,通过多项式除法检测错误,是在数据通信和数据检测中广泛应用的检错校验的循环码。

本设计研究了CRC循环冗余校验码的原理,以及利用C语言对其进行了编程和编译仿真,实现了CRC循环冗余校验码的编码及校验,在接收端收到通过校验的码,从而确定传输过程是否出错,得到的结论和理论上是一致的。

关键词:检错码;CRC循环冗余校验码;C语言前言随着科学技术的进步, 人们对信息传递的要求逐渐提高。

但在通信系统中, 可靠性与有效性是对矛盾, 要求有效性提高, 必然使每个码元所占的时间缩短, 从而受干扰和产生错误的可能性增大, 可靠性降低了; 要提高信息的可靠性,又使信息速率变慢有效性降低。

在实际信道上传输数字信号时,由于信道传输特性不理想及加性噪声的影响,所收到的数字信号不可避免的会发生错误。

为了加强通信系统的可靠性,除了合理设计基带信号,选择调制、解调方式,采用频域均衡、时域均衡之外,还需要采用信道编码,即差错控制编码,使误码率进一步降低,来满足指标要求。

循环冗余校验码CRC(Cyclical Redundancy Checking)是目前通信系统中最常用的一种差错控制编码。

循环冗余校验码是一种高效率且可靠的方法, 由线性分组码分支而来的, 是一种通过多项式除法检测错误的很不寻常而又巧妙的方法, 一方面它有很强的检测能力, 二是它的编码器电路及错误检测器电路都很容易实现, 它的优点使它在通信系统中得到了广泛的应用。

利用CRC进行检错的过程可简单描述为:在发送端根据要传送的二进制码序列,以一定的规则产生一个校验用的监督码(CRC码),附在原始信息后边,构成一个新的二进制码序列数,然后发送出去。

基于MATLAB的卷积交织编译码研究

基于MATLAB的卷积交织编译码研究

姚远程;廖祥

【期刊名称】《西南科技大学学报》

【年(卷),期】2004(019)003

【摘要】介绍了卷积码的特点以及卷积码的编码和解码,讨论了加入交织后的对卷积编码的误码率的改善情况,并使用MATLAB进行DPSK通信系统中卷积编译码和卷积码+块交织的编译码仿真.

【总页数】4页(P11-14)

【作者】姚远程;廖祥

【作者单位】西南科技大学信息与控制工程学院,四川,绵阳,621010;西南科技大学信息与控制工程学院,四川,绵阳,621010

【正文语种】中文

【中图分类】TN919.3

【相关文献】

1.基于FPGA的卷积码编译码器 [J], 张有志;张鹍

2.基于FPGA的卷积编译码器的设计与实现 [J], 刘杨;章敏

3.基于卷积面向分组Turbo码的交织器研究 [J], 李苏萍;徐澄圻

4.卷积码编译码的Matlab仿真及其性能研究 [J], 吴亚婷

5.基于EAB资源的交织编译码器的设计与实现 [J], 胡辛

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

西南科技大学方向设计报告课程名称:通信工程方向设计设计名称:2/3卷积码编译码器仿真与性能分析姓名:学号:班级:指导教师:起止日期:2011.12.12-2012.1.6西南科技大学信息工程学院制方向设计任务书学生班级:学生姓名:学号:设计名称:2/3卷积码编译码器仿真与性能分析起止日期:2011.12.12-2012.1.6指导教师:设计要求:(1)分析2/3卷积码编码器结构;(2)分析2/3卷积码译码的Viterbi算法;(3)基于SIMULINK进行2/3卷积码的纠错性能仿真;方向设计学生日志时间设计内容12.15-12.17 查看题目及设计要求。

12.18-12.23 查阅相关资料,设计方案。

12.23-12.27 编写报告及调试程序。

12.28-12.29 完善修改课程设计报告。

12.30-12.31 答辩。

方向设计考勤表周星期一星期二星期三星期四星期五方向设计评语表指导教师评语:成绩:指导教师:年月日2/3卷积码编译码器仿真与性能分析摘要:卷积码是一种性能优越的信道编码。

它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

本文简明地介绍了卷积码的编码原理和Viterbi译码原理。

并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。

最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。

经过仿真和实测,并对测试结果作了分析。

关键词:卷积码编码器、viterbi译码器、SIMULINK目录一设计目的和意义........................................... 错误!未定义书签。

二设计方法................................................. 错误!未定义书签。

三设计原理................................................. 错误!未定义书签。

3.1 卷积码的基本概念 (1)3.2 卷积码的结构 (2)3.3 卷积码的图解表示 (3)3.3.1 卷积码的树状图 (3)3.3.2 卷积码网格图 (4)3.4卷积码的解析表示 (4)3.5 卷积码的译码 (5)3.5.1 卷积码译码的方式 (5)3.5.2 卷积码的viterbi译码 (6)四 SIMULINK下的仿真设计 (7)4.1 SIMULINK下卷积码的仿真 (7)4.1.1 SIMULINK仿真模块参数设置及意义 (8)4.2 改变卷积码参数分析 (17)4.2.1 回溯长度对卷积码的影响........................ 错误!未定义书签。

4.2.2 约束长度对卷积码的影响 (19)五心得体会................................................. 错误!未定义书签。

六参考文献................................................. 错误!未定义书签。

一、设计目的和意义因为信道中信号不可避免会受到干扰而出错。

为实现可靠性通信,主要有两种途径:一种是增加发送信号的功率,提高接收端的信号噪声比;另一种是采用编码的方法对信道差错进行控制。

前者常常受条件限制,不是所有情况都能采用。

而编码理论可以解决这个问题,使得成本降低,实用性增强。

随着现代通信的发展,卷积码以其高速性和可靠性在实际应用中越来越广泛。

1967年Viterbi译码算法的提出,使卷积码成为信道编码中最重要的编码方式之一。

在卷积码中,因为Viterbi算法效率高,速度快,结构相对简单等特点,被广泛应用于各种数据传输系统。

特别是深空通信、卫星通信系统中。

因此采用Viterbi译码算法具有非常现实的意义。

二、设计方法本文在分析卷积码编译码器原理的基础上,通过基于MATLAB的SIMULINK下的模块对卷积编码,解码进行仿真。

通过仿真可以更清楚的认识到卷积码的编码,解码的各个环节,并对仿真结果进行了分析。

得出卷积码Viterbi译码的误比特性能和回溯长度,码率,约束长度的关系。

三、设计原理3.1 卷积码基本概念卷积码是一种性能优越的信道编码。

(n ,k ,N) 表示把k个信息比特编成n 个比特,N 为编码约束长度,说明编码过程中互相约束的码段个数。

卷积码编码后的n 个码元不仅与当前组的k 个信息比特有关,而且与前N - 1 个输入组的信息比特有关[6]。

编码过程中相互关联的码元有N ×n 个。

R = k/ n 是卷积码的码率,码率和约束长度是衡量卷积码的两个重要参数。

卷积码的编码描述方式有很多种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述,树图描述,网格图描述等。

卷积码的纠错能力随着N的增加而增大,而差错率随着N的增加而指数下降。

在编码器复杂性相同的情况下,卷积码的性能优于分组码。

分组码的译码算法可以由其代数特性得到。

卷积码虽然可以采用适用于分组码的门限译码(即大数逻辑译码),但性能不如维特比译码和序列译码3.2 卷积码的结构图2-1卷积码的编码器一般都比较简单。

下图2-1是一般情况下的卷积码编码器框图。

它包括:一个由N段组成的输入移位寄存器,每段有k级,共Nk位寄存器;一组n个模2和相加器;一个由n级组成的输出移位寄存器。

对应于每段k个比特的输入序列,输出n个比特。

由图可知,n个输出比特不但与当前k个比特的输入比特有关,而且与以前的(N-1)k个输入信息有关。

整个编码过程可以看成是输入信息序列与由移位寄存器和模2加法器的连接方式所决定的另一个序列的卷积,卷积码由此得名。

图2-2如图2-2是卷积码(3,2,2)卷积编码器的一个框图。

左边是信息的输入。

下面分别是系统位输出和校验位输出。

其中间是四个移位寄存器和三个模2加法器。

简单的说就是信息位经过移位寄存器和一个模2加法器产生一个系统位和校验位加在一起输出。

可以看出:每输入一个比特,移位寄存器中就向右移动一个位子。

原来的第四个寄存器就被移出。

可见卷积编码不只与现在的输入比特有关还与前面的1个比特有关。

在这里,其中约束长度是N=2,k=2 ,n=3所以码率R=k/n=2/3。

3.3 卷积码的图解表示3.3.1 卷积码的树状图对于图2-2所示的(3,2,2)卷积码编码电路,其树状图如下图2-3所示。

若寄存器初始状态为全0,第一组输入的两个信息比特可以是:00,01,10,11,与他们对应的输出比特是000,010,111,101。

第二组两个输入比特进入移位寄存器时,第一组两个输入比特右移到右边那组寄存器,此时输出比特不但取决于当前的二个输入比特,而且取决于第一组的二个输入比特。

由于每组输入两个比特,因此树状图每个节点有2的平方条支路。

由于约束长度为2从第二级后开始重复出现4种状态,可以得到整个树状图。

如下图2-3图2-33.3.2 卷积码的网格图如下图2—4是(3,2,2)卷积编码的网格图。

图2-4 (3,2,2)卷积编码的网格图图2-5 (3,2,2)卷积码的状态图3.4 卷积码的解析表示除上述图解表示方法外,常常还用解析表示方法描述卷积码,即延时算子多项式。

在延时算子多项式表示中,编码器中的移位寄存器与模2加法器的连接关系以及输入、输出序列都表示为延时算子D 的多项式。

在一般情况下,输入序列可表示为:...M(D)2321D m D m m ++= (2-1)变量D 的幂的次数等于相对于时间起点的单位延时数目,时间起点通常选在第1个输出比特,ml,m2,m3,m...为输入比特的二进制表示(1或0)。

用D 算子多项式表示移位寄存器各级与各模2项连接关系时。

若某级寄存器与某模2和相连,则多项式中相应项的系数为1,否则为0(表示无连接)。

通常把表示移位寄存器与模2和连接关系的多项式称为生成多项式,因为由它们可以用多项式相乘计算出输出序列。

卷积码的图解与解析表示方法各有特点。

用延时算子多项式表示卷积码编码器的生成多项式最为方便。

网格图对于分析卷积码的译码算法十分有用。

3.5 卷积码的译码 3.5.1 卷积码译码的方式卷积码的译码方式有三种:(1)1963年由梅西((Massey)提出的门限译码,这是一种基于码代数结构的代数译码,类似于分组码中的大数逻辑译码;(2) 1963年由费诺(Fano)改进的序列译码,这是基于码的树状图结构上的一种准最佳的概率译码;(3) 1967年由维特比提出的Viterbi 算法。

这是基于码的网(trellis)图基础上的一种最大似然译码算法,是一种最佳的概率译码方法。

其中,代数译码,利用编码本身的代数结构进行译码,不考虑信道本身的统计特性。

该方法的硬件实现简单,但性能较差,其中具有典型意义的是门限译码。

另一类是概率译码,这种译码通常建立在最大似然准则的基础上。

由于计算是用到了信道的统计特性.因而提高了译码性能,但这种性能的提高是以增加硬件的复杂度为代价的。

常用的概率译码方法有维特比译码和序列译码。

维特比译码具有最佳性能,但硬件实现复杂;门限译码性能最差,但硬件简单;序列译码在性能和硬件方面介于维特比译码和门限译码之间。

3.5.2 卷积码的Viterbi译码卷积码概率译码的基本思路是:以接收码流为基础,逐个计算它与其他所有可能出现的、连续的网格图路径的距离,选出其中可能性最大的一条作为译码估值输出。

概率最大在大多数场合可解释为距离最小,这种最小距离译码体现的正是最大似然的准则。

卷积码的最大似然译码与分组码的最大似然译码在原理上是一样的,但实现方法上略有不同。

主要区别在于:分组码是孤立地求解单个码组的相似度,而卷积码是求码字序列之间的相似度。

基于网格图搜索的译码是实现最大似然判决的重要方法和途径。

用格图描述时,由于路径的汇聚消除了树状图中的多余度,译码过程中只需考虑整个路径集合中那些使似然函数最大的路径。

如果在某一点上发现某条路径已不可能获得最大对数似然函数,就放弃这条路径,然后在剩下的“幸存”路径中重新选择路径。

这样一直进行到最后第L级(L 为发送序列的长度)。

由于这种方法较早地丢弃了那些不可能的路径,从而减轻了译码的工作量,Viterbi译码正是基于这种想法。

对于(n, k, K )卷积码,其网格图中共2kL种状态。

由网格图的前K-1条连续支路构成的路径互不相交,即最初2k_1条路径各不相同,当接收到第K条支路时,每条路径都有2条支路延伸到第K 级上,而第K级上的每两条支路又都汇聚在一个节点上。

在Viterbi译码算法中,把汇聚在每个节点上的两条路径的对数似然函数累加值进行比较,然后把具有较大对数似然函数累加值的路径保存下来,而丢弃另一条路径,经挑选后第K级只留下2K条幸存路径。