反相器版图

硅栅P阱CMOS反相器版图设计举例刻NMOS管S

n+区/保护带

P+区保护环

版图分解: 1. 刻P阱 2. 刻P+区/保护环 3. 刻n+区/保护带 4. 刻栅、预刻接触孔 5. 刻接触孔 6. 刻Al 7. 刻纯化孔

图2 铝栅CMOS反相器版图示意图

版图分解: 1. 刻P阱 2. 刻P+区/环 3. 刻n+区 4. 刻栅、预刻接触孔 5. 刻接触孔 6. 刻Al 7. 刻纯化孔

3

版图分解: 1. 刻P阱 2. 刻P+区/环 3. 刻n+区 4. 刻栅、预刻接触孔 5. 刻接触孔 6. 刻Al 7. 刻纯化孔

4

4) 硅栅MOS版图举例 E/E NMOS反相器 刻有源区 刻多晶硅栅 刻NMOS管S、D 刻接触孔 反刻Al

图5 E/E NMOS反相器版图示意图

5. 刻NMOS管 S、 D T1 W/L=1/1

Poly Diff Al con

Vdd

P阱

Vi

Vo

6. 刻接触孔 7. 反刻Al (W/L)p=3(W/L)n

Vss

1. 刻P阱

2. 刻有源区

3. 刻多晶硅栅

4. 刻PMOS管S、D

5. 刻NMOS管S、D

6. 刻接触孔

VDD

7. 反刻Al

VDD

E/D NMOS 反相器

刻有源区 刻耗尽注入区 刻多晶硅栅 刻NMOS管S、D 刻接触孔 反刻Al

图6 E/D NMOS 反相器版图

制备耗尽型MOS管

在MOS集成电路中,有些设计需要 采用耗尽型MOS管,这样在MOS工艺过 程中必须加一块光刻掩膜版,其目的是 使非耗尽型MOS管部分的光刻胶不易被 刻蚀,然后通过离子注入和退火、再分 布工艺,改变耗尽型MOS管区有源区的 表面浓度,使MOS管不需要栅电压就可 以开启工作。 然后采用干氧-湿氧-干氧的方法 进行场氧制备,其目的是使除有源区部 分之外的硅表面生长一层较厚的SiO2层, 防止寄生MOS管的形成。

集成电路课程设计--cmos反相器的电路设计及版图设计

目录摘要 (3)绪论 (5)1软件介绍及电路原理 (6)1.1软件介绍 (6)1.2电路原理 (6)2原理图绘制 (8)3电路仿真 (10)3.1瞬态仿真 (10)3.2直流仿真 (11)4版图设计及验证 (12)4.1绘制反相器版图的前期设置 (12)4.2绘制反相器版图 (13)4.3 DRC验证 (15)结束语 (17)参考文献 (18)摘要CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。

集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。

本文将简单的介绍基于ORCAD和L-EDIT的CMOS反相器的电路仿真和版图设计,通过CMOS反相器的电路设计及版图设计过程,我们将了解并熟悉集成电路CAD的一种基本方法和操作过程。

关键词:CMOS反相器ORCAD L-EDIT版图设计AbstractThe huge development potential of CMOS technology itself is the foundation of sustainable development of IC high speed. The manufacturing level of development of the integrated circuit to the deep sub micron technology, CMOS low power consumption, high speed and high integration have been fully reflected. In this paper, the circuit simulation and layout design of ORCAD and L-EDIT CMOS inverter based on simple introduction, through the circuit design and layout design process of CMOS inverter, we will understand and a basic method and operation process, familiar with IC CAD.Keywords: CMOS inverter layout ORCAD L-EDIT绪论20世纪是IC迅速发展的时代。

实验九:使用L-Edit编辑反相器的版图

出现的对话框的 From file 下拉列表右侧的 Browser 按钮,选择 d:\My Documents\Tanner EDA\Tanner Tools v13.0\L-Edit and LVS\SPR\Lights\Layout\lights.tdb 文件, 如图所示, 再单击 OK 按钮。 接着出现一个警告对话框, 按确定按钮, 就可将 lights.tdb 文件的设定选择性应用在 目前编辑的文件,包括格点设定、图层设定等。 5.重新命名:将 Cell0 的名称重新命名,可选择 Cell Rename 命令,打开 Rename Cell Cell0 对话

四、实验报告要求

实验报告包括以下内容: 1.绘制反相器版图的详细步骤; 2.在进行 DRC 检查过程中出现的错误; 3.绘制的版图; 4.绘制过程中出现的问题; 5.实验中的心得与体会。

五、反相器

1.真值表: A 0 1 Y 1 0

2.逻辑表达式: Y A

1

3.电路图:4.版图: Nhomakorabea2

六、操作步骤:

5

例使用技术设定为 MOSIS/ORBIT 2.0U SCNA Design Rules,输入输出信号由 Metal2 传入,故一个反相器 输入端口需要绘制 Metal2 图层、 Via 图层、 Metal 1 层、 Poly Contact 图层与 Poly 图层, 才能将信号从 Metal2 图层传至 Poly 层。 具体操作是: 先绘制 2 2 格点的 Poly Contact 图层, 然后在 Poly Contact 上面绘制一层 5 5 格点的 Poly 图层, Poly Contact 是用来连 接 Poly 层和 Metal 1 的接触孔,故接着绘制一个 10 4 格点的 metal 1 图层,接下来在 Metal 1 上绘制 2 2 格点的 Via(通孔)图层,Via 图层是用来连接 Metal 1 和 Metal 2 的接触孔。所以最后在 Via 上绘制 4 4 格点的 Metal 2 图层。绘制结果 如图所示。 14.新增输出端口 output 元件:选择 Cell 文本框中输出“output” ,单击 OK 按钮。 15.编辑输出端口 output 元件:反相器有一个输出端口,输出信号是从漏极输出,由 于此范例使用技术设定为 MOSIS/ORBIT 2.0U SCNA Design Rules,输入输出信号由 Metal 2 传出,故可在连接 pmos 与 nmos 漏极区的 Metal 1 上绘制 Via 图层与 Metal2 图 层,才能将漏极信号从 Metal 1 图层传至 Metal2 图层。 Via 图层是用来连接 Metal 1 图层与 Metal2 图层的接触孔。 具体操作是: 先绘制 2 2 格点的 Via 图层, 接着绘制 4 4 格点的 Metal2 图层,它要与 Via 图层重叠。绘制结果如图所示。 16.引用 Basecontactp、Basecontactn、input、output 元件:先选择 Cell 点击 OK 按钮, 回到 inv 编辑面板中。 然后选择 Cell open 命令,选择 inv 单元元件, New 命令,打开 Create New Cell 对话框,在 New cell name

CMOS反相器版图设计

XXXXXXX实验报告课程名称:集成电路设计实验名称:CMOS反相器版图设计学号姓名:指导教师评定:____________________________ 签名:_____________________________一、实验目的1、了解集成电路版图设计流程。

2、利用L-Edit 进行NMOSFET 版图设计。

3、利用L-Edit 进行CMOS反相器设计。

二、实验器材计算机一台,Tanner L-Edit软件三、实验原理CMOS 反相器由PMOS 和NMOS 晶体管组成,利用PMOS晶体管版图和NMOS 晶体管版图可以完成COMS反相器版图的设计。

四、实验步骤1、设计PMOS晶体管版图。

2、设计N MOS晶体管版图。

3、设计CMOS反相器版图:(1)启动版图编辑器L-Edit。

(2)新建文件。

新建一个Layout 文件,文件的设置信息可以从前面创建的文件中复制。

(3) 对文件进行重命名。

将L-Edit 编辑器默认的文件名Layout 改为Inverter。

(4) 设置格点与坐标。

格点与坐标的设定方式与创建PMOS 晶体管时设定的方法一致。

(5) 调用PMOS 和NMOS 晶体管作为例化单元。

使用Cell---Instance 命令来调用PMOS 单元。

在出现的Select Cell to Instance 对话框中,通过点击Browse按钮浏览到“MOS”文件,可以看到该文件下面有PMOS 和NMOS 两个单元,点击PMOS,然后点击“OK”,可以看到Inverter 文件cell0 单元的版图已经添加了PMOS 单元。

利用同样的方法,可以将NMOS 单元也添加进来。

(6) 连接PMOS 和NMOS 晶体管的栅极。

从CMOS 反相器电路可知,PMOS晶体管和NMOS 晶体管的栅极要连在一起作为反相器的输入端,所以在放置这两个晶体管的时候可以将两者的栅极对准,以便连接。

具体操作是,选择Layer的多晶硅(Poly)层和方框绘图工具后,在版图区域中画一个宽度与晶体管栅极相等的多晶硅矩形,如图1 所示。

CMOS反相器原理图版图的仿真设计

集成电路专业学年论文论文题目:CMOS反相器原理图版图设计与仿真学院:电子工程学院年级:2008级专业:集成电路设计与集成系统姓名:学号:指导教师:2011年 7月 8日摘要门电路是构成各种复杂数字电路的基本逻辑单元,掌握各种门电路的逻辑功能和电气特性,对于正确使用数字集成电路是十分必要的。

MOS门电路:以MOS管作为开关元件构成的门电路。

MOS门电路,尤其是CMOS门电路具有制造工艺简单、集成度高、抗干扰能力强、功耗低、价格便宜等优点,得到了十分迅速的发展。

所谓CMOS (Complementary MOS),是在集成电路设计中,同时采用两种MOS器件:NMOS和PMOS,并通常配对出现的一种电路结构。

CMOS电路及其技术已成为当今集成电路,尤其是大规模电路、超大规模集成电路的主流技术。

反相器是数字电路中的一种基本功能模块。

将两个串行反相器的输出作为一位寄存器的输入就构成了锁存器。

锁存器、数据选择器、译码器和状态机等精密数字符件都需要使用基本反相器。

因此此次针对CMOS反相器原理图、版图设计与仿真也是很有必要的自己学会了Tanner EDA软件的使用。

也进一步了解了CMOS反相器直流特性瞬态特性和版图的绘制。

关键词CMOS;反相器;Tanner EDA;设计;仿真;版图;AbstractThe complex digital circuits are constituted by the basic gate circuits,and the Gate circuits is the logic cells.Grasp at various kinds of logic gates' functions and electrical characteristics for the proper use of digital integrated circuits is essential. MOS gate[1]: The MOS tube as a switching element constitute the gate. MOS gate, especially a CMOS gate with simple manufacturing process, high integration, anti-interference ability, low power consumption, cheap, etc., has been very rapid development. The so-called CMOS (Complementary MOS), is in IC Design, while using two MOS devices: NMOS and PMOS, and the emergence of a circuit is usually paired structure. CMOS circuits and technology has become today's integrated circuits, especially large-scale circuits, VLSI mainstream technology.Inverter is a basic digital circuit modules. The two serial output of the inverter as a register input to constitute a latch. Latch, data selectors, decoders and state machines and other precision parts are required to use a few characters in the basic inverter.Therefore, the schematic for the CMOS inverter layout design and simulation is necessary to learn their own Tanner EDA software. Further understanding of the transient characteristics of CMOS inverter DC characteristics and layout drawing.Key wordsCMOS; inverter; TannerEDA; design; simulation; territory;目录摘要 (II)Abstract (III)前言 (3)第一章使用S-Edit编辑设计CMOS反相器原理图 (4)1.1绘制CMOS反相器原理图 (4)1.1.1进入S-Edit建立新文件 (4)1.1.2环境设置环境设置 (4)1.1.3编辑模块并浏览组件库 (5)1.1.4从组件库引用模块 (5)1.1.5编辑反相器 (6)1.1.6加入输入输出端口 (7)1.1.7反相器的输出成果 (7)1.2反相器瞬态分析 (8)1.2.1进入S-Edit编辑文件 (8)1.2.2输出成Spice文件 (8)1.2.3加载包含文件 (9)1.2.4插入分析设定和输出设定命令 (10)1.2.5进行模拟 (11)1.3反相器直流分析 (12)1.3.1 进入S-Edit (12)1.3.2 加入工作电源和输入直流信号 (12)1.3.3 编辑直流电压源 (13)1.3.4 输出spice文件 (13)1.3.5分析设定和输出设定 (14)1.3.6进行模拟 (115)1.3.7结果分析 (116)第二章使用S-Edit编辑设计CMOS反相器原理图 (17)2.1绘制反相器版图的前期设置工作 (17)2.1.1 打开L-Edit软件新建版图文件 (17)2.1.2 取代设定 (17)2.1.3编辑组件 (17)2.1.4设计环境设定 (17)2.2绘制反相器 (18)2.2.1 编辑PMOS (18)2.2.2 编辑NMOS (18)2.2.3 其他部分 (20)2.3使用T-Spice进行版图设计仿真 (21)结论 (22)参考文献 (23)前言CMOS结构的主要优点是电路的静态功耗非常小,电路结构简单规则,使得它可以用于大规模集成电路、超大规模集成电路。

集成电路版图设计项目教程 项目3 反相器版图设计

Assura和Mentor的Calibre验证工具等。

2022/3/19

项目3 反相器版图设计

➢ 2.Pitch计算用金属布线通孔与通孔的距离。这时,Pitch值 的计算公式为最小间距(0.5μm) + 2倍的金属布线M2包围通 孔的最小包围0.15μm + 布线宽度(0.6μm)=1.4μm。

➢ 3.Pitch计算用金属布线中心线与通孔的距离。这时,Pitch 值的计算公式为最小间距(0.5μm) + 1倍的金属布线M2包围 通孔的最小包围0.15μm + 布线宽度(0.6μm)=1.25μm。

1.PDK主要包含: ➢ 1.器件模型(Device Model):由Foundry提供的仿真模型文件; ➢ Symbols & View:用于原理图设计的符号,参数化的设计单元都通过了Spice仿真的验证; ➢ 2.CDF(Component Description Format,组件描述格式) & Callback:器件的属性描述文件,定义了器件类型、

器件名称、器件参数及参数调用关系函数集Callback、器件模型、器件的各种视图格式等; ➢ 3.Pcell(Parameterized Cell,参数化单元):它由Cadence的Skill语言编写,其对应的版图通过了DRC和LVS

验证,方便设计人员进行Schematic Driven Layout(原理图驱动的版图)设计流程; ➢ 4.技术文件(Technology File):用于版图设计和验证的工艺文件,包含GDSII的设计数据层和工艺层的映射

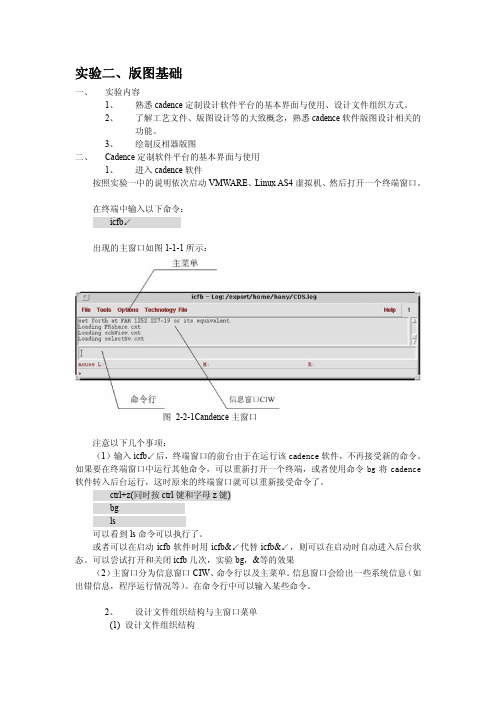

实验二——反相器版图绘制

然后会弹出设置 Technology 库的窗口,选中 csmc_tf,然后“OK”

这样,一个新的设计库“test1”就建好了。主窗口中 ToolsàLibrary Manager,会看到 Library 列表中增加了一个新的库“test1”。选中该库(鼠标左键在窗口中点击 test1),会看 到 cell 和 view 两栏都是空白的,这是因为这个库中目前还没有任何设计单元存在。

IM

第二层多晶硅电阻阻挡层

PC poly Cap,用作多晶硅电容上极板和多晶硅电阻的第二层多晶硅

详细的工艺信息请参考设计规则(0.6umDPDMMixedSignalTechnologyTopological DesignRule.pdf),本次实验将会用到的层为 TB、TO、GT、SP、SN、W1、A1、W2、A2

需要选中显示的图层包括前面第四部分列出的设计图层:TB、TO、GT、SP、SN、W1、A1、 W2、A2,以及用于标记的 A1TEXT、A2TEXT、TEXT、boarder、prBoundry层。(注意:应被 选择的是后面标记为“dg”的层)

选择完成后,点击“OK”。

完成以上操作后,可以看到 LSW 窗口中变为只显示所设置的图层了。

设置图层的颜色图案:LSW 窗口中选中 EditàDisplay Resource Editor,会出现一个 “Display Resource Editor”窗口,在这里可以改变图层的颜色和图案。由于时间关系,本次 实验中不进行该操作,有兴趣的同学可以在完成实验后自己进行操作。

(4)、Layout 窗口介绍: 版图窗口由三部分组成:Icon menu , menu banner , status banner. Icon menu (图标菜单)缺省时位于版图图框的左边,列出了一些最常用的命令的图标,要 查看图标所代表的指令,只需要将鼠标滑动到想要查看的图标上,图标下方即会显示出相应 的指令。 menu banner(菜单栏),包含了编辑版图所需要的各项指令,并按相应的类别分组。 status banner(状态显示栏),位于 menu banner 的上方,显示的是坐标、当前编辑指令 等状态信息。 请熟悉一下版图编辑窗口中各个部分的状态,功能,以及菜单和图标对应的内容。随 后的反相器版图设计工作将主要在该窗口中进行。

CMOS反相器的版图设计

CMOS反相器的版图设计实验一:CMOS反相器得版图设计一、实验目得1、创建CMOS反相器得电路原理图(Schematic)、电气符号(s ymbol)以及版图(layout);2、利用’gpdk090’工艺库实例化MOS管;3、运行设计规则验证(Design Rule Check,DRC)确保版图没有设计规则错误。

二、实验要求1、打印出完整得CMOS反相器得电路原理图以及版图;2、打印CMOS反相器得DRC报告。

三、实验工具Virtuoso四、实验内容1、创建CMOS反相器得电路原理图;2、创建CMOS反相器得电气符号;3、创建CMOS反相器得版图;4、对版图进行DRC验证。

1、创建CMOS反相器得电路原理图及电气符号图首先创建自己得工作目录并将/home/iccad/cds、lib复制到自己得工作目录下(我得工作目录为/home/iccad/iclab),在工作目录内打开终端并打开virtuoso(命令为icfb &)。

在打开得icfb–log中选择tools—>LibraryManager,再创建自己得库,在当前得对话框上选择File-〉New->Library,创建自己得库并为自己得库命名(我得命名为lab1),点击OK后在弹出得对话框中选择Attach to an exiting techfile并选择gpdk090_v4、6得库,此时Library manager 得窗口应如图1所示:图1 创建好得自己得库以及inv创建好自己得库之后,就可以开始绘制电路原理图,在Library manager窗口中选中lab1,点击File—〉New->Cell view,将这个视图命名为inv(CMO S反相器)、需要注意得就是Library Name一定就是自己得库,ViewName就是schematic,具体如图2所示:图2inv电路原理图得创建窗口点击OK后弹出schematic editing得对话框,就可以开始绘制反相器得电路原理图(schematic view)、其中nmos(宽为120nm,长为100nm。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录

一、课程设计的目的 (2)

二、用Cadence软件画CMOS反相器的版图 (2)

三、心得体会 (4)

一、课程设计的目的

1、学习对LINUX Cadence软件的使用。

2、了解反相器版图的结构及工作原理。

3、了解版图设计规则。

二、用Cadence软件画CMOS反相器的版图

1、CMOS反相器的原理图

CMOS反相器的原理

CMOS反相器由PMOS和NMOS构成,当输入高电平时,NMOS导通,输出低电平,当输入低电平时,PMOS导通,输出高电平。

IN OUT

0 1

1 0

2、画版图

首先建立自己的文件夹并导入库文件,运行Cadence,如图

在其中建立自己的工艺库、设计库和版图库,再用自己的库打开画版图的界面,如图

绘制版图如图

步骤:PSUB→NWELL→ACTIVE→POLY1→NIMP→PIMP→CONTACT→METAL1

PSUB —NWELL —

ACTIVE —POLY —

NIMP—PIMP—

CONTACT—METAL1 —

3、改进意见及建议

(1)画成插齿形状,增大了宽长比,可以提高电路速度

(2)尽可能使版图面积最小。

面积越小,速度越高,功耗越小。

(3)尽可能减少寄生电容和寄生电阻。

尽可能增加接触孔的数目可以减小接触电阻。

(4)尽可能减少串扰,电荷分享。

做好信号隔离,添加隔离环。

三、心得体会

通过这次课程设计,我学会了怎么运用LINUX和Cadence的一些基本操作做一个反相器的IC版图,也学会了实际画版图时应注意哪些细节,增强了我的实际操作能力,希望以后多多设置这样的课设。