Circuit Optimization Using Carry–Save–Adder Cells

phy_design_interview

CONSTRAINTSDo you know synthesis and timing constraints?Yes.Explain one each?Synthesis is the process to translate verified RTL code to a logical equivalent logic netlist for a targeted tech library. A synthesis script includes the following data/filesRTL + timing library + timing constraints + syn directives => netlistTiming constraints are the set of constraints in order for the chip to meet certain timing goal. It often uses the following constructs:create_clock: create a clock and specify clock root pin, period, clock duty cycle, arrival time, uncertaintycreate_generated_clock :set_load: output load cap(seldom use)set_driver_cell: driver cell strength to the input of this block(seldom use)Explain input and output delays?Set_input_delay: input arrives after the specified time period with respect to a clock Example: set_input_delay 4 -clock "usbclk" [get_ports {USB_data[0]}]Set_output_delay: output leaves after the specified time period with respect to a clock Example: set_output_delay 30 -clock "smci_clk" [get_ports {nSMCI_RST}]Explain multicycle and false paths?1) Set_multicycle_path: specify the path between 2 flops can be finished in multiple cycles of the specified clock.Example1: set_multicycle_path 2 –setup -from [get_clocks {hclk}] -to [get_clocks {aclk}] Example 2: set_multicycle_path 1 -hold –end -from [get_clocks {hclk}] -to [get_clocks {aclk}]Example 3: set_multicycle_path 2 -setup –start -from [get_pins{core_i/clkcntl/i_hclken_reg/CK}] -to [get_clocks {aclk}]Example 4: set_multicycle_path 1 –hold -from [get_pins{core_i/clkcntl/i_hclken_reg/CK}] -to [get_clocks {aclk}]2) set_false_pathpath needed not be checked for timing. It is often used in asyn signal such as reset and signals between 2 clock domains.Example: set_false_path -from [get_clocks {ETH_TX_CLK}] -to [get_clocks {aclk}] What is case analysis?Specify the mux selection path needed to be optimizedset_case_analysis 1 [get_pins {dsp/clkenb}]SYNTHESISExplain a typical synthesis script/flow?1) RTL code development from specification2) RTL code logic verification (testbench against a golden model usually in a higher level of language)3) Synthesis the verified RTL code with timing constraints, synthesis directives to a target technology/IP library. The result is gate level netlist; formal verification of the netlist against the RTL code4) STA5) yes, DFT6) no, fix timing violation , STA and DFTWhat is a generic netlist?library independent netlistrtl -> z = e & f ;generic netlist -> and U1 (.A(e) .B(f) .x(z))"and" here is a technology independent generic and gate.mapped netlist -> SDN_AND21_4 U1 (.A(a), .B(f) .X(Z))SDN_AND21_4 is an and gate from the target library, in this case viragethe flow is rtl -> generic netlist -> mapped netlistonly during mapping you need a library. all generic libararies come with the synthesis tool.What is mapping?Map the generic netlist to target technology based netlistWhat are the pros and cons of POS and SOP?POS: product of sumSOP: sum of productArea vs. timingHow do you get routing estimates in Synthesis?Use wire load model(WLM)What are the problems of Wire Load Models?The wire load is statistic load and the synthesized gate netlist is based on these statistic load. When gate delay dominates, WLM is a good estimate and timing closure is predictable. While in deep submicro (0.18um and below), since wire delay dominates, WLM is not a good estimate and timing closure based solely on WLM is very hard. Solution: physical synthesis and silicon virtual prototyping to better represent the actual wire.What is scan chain stitching?yes. It is the process of converting all flops in the design to scannable flops and hooking up Q->SI and inserting muxes at the end of each chain etc.or in other words test synthesisWhat is datapath synthesis?regular synthesis - control logic rtl -> gatesdatapath synthesis -> arthemetic logic rtl -> gatesinput a [32:0]input b [32:0]z = a + babove will become a ripple carry adder if done by regular synthesis.datapath synthesis will choose from Carry Save, Carrylookahead, Carry Select, ripple etc.and give smaller or faster designssamething with booth multiplier etc.How does the tool identify datapath objects?if Ambit(cadence) or RC (cadence) compileranytime the following operators are used, it triggers datapath synthesis for those modules.<<< >>> + * / and othersi.e. your rtl can have the above and the same do_optimize command will automatically partition you design into datapath and control logic. and during the whole optimization flow it switches between regular and datapath depending on where the timing problem is. i.e. one engine. which is timing concious.and since rtl can be simulated. and a single module can have both arthmetic and logic functions.the way it triggres is as soon as it sees any of those operators it creates a new hier. called AWDP_ with that logic inthere. of course 100's of swithces to control.if synopsys.you have to write your arthmetic logic in module (manual partitioning) using module compiler language (MCL)give this to the tool called module compiler. get the netlist. and instantiate it in your regular rtl. and use regular synthesis from now on.manual hier partitioning.learn new language(MCL)new toola single module cannot have both control and data.not timing conscious as timing constraints cannot be read into MCLduring optimization you can only use regular synthesis to fix datapath problems.no simulations etc are possible as MCL is not accepted by any simulator.Why is datapath synthesis needed?Because datapath is often timing critical path, the synthesis result directly affects timing closure.Name some optimization algorithms?the question should be more like the techniques/optimizations during meeting timingfast buffer insertion,constant propagationredundancy removalcontext based component swapping. (based on timing, a ripple carry adder is swapped with carry save to meet timing)restructuringmapping (to target technology from generic netlist based on area or timing) boundary optimizationetc.What is design rule fixing in synthesis?Fanout, fanin, transition time, hold. Syn tool tries to meet these constraints.What do you do for very large fanout nets?Insert buffer and create buffer treesmake sure they are not inserted during synthesis.backend should take care of that.in FE4.2 no need to use clocktree etc to build buffer trees.regular optimization will take of these automatically for you.it is important to make sure synthesis did not already build themif it did you have to remove either in synthesis remove_buffer_tree or in FE What is formal verification?Without providing testbench and running simulation, mathematically prove 2 logic implementation (such as RTL vs gate level netlist) is logic equivalentTIMINGWhat is the difference between static and dynamic timing analysis?Static dynamicInput constraint input stimuli to exercise the critical path Netlist gate level netlist, gate transistor leveltiming is pre-characterizedaccuracy less accuracy due to limited timing most accuratetablecoverage through and all paths only good if the input stimuli run time short longcircuit type static CMOS any type(static CMOS, NMOS, domino etc)What is PVT or operating conditions?PVT: process corner, operation voltage and temperatureHow are rise/fall transitions calculated?Rise = 0.9 * high level – 0.1 * low levelFall = 0.1 * low level – 0.9 * high levelHow do you measure propagation delay?Give input stimuli and measure 50% transition time from input change to the output changeWhat are timing tables?For a pre-characterized cell, the output delay, output slew, setup and hold, power etc is calculated as in a matrix or one row form for the given sets of value of related inputs. the related table headings areinput slew and output loadExplain dependencies of delay and output slew of comb cells?nope.output slew depends on input slew and output load.propagation delay thru the cell depends on input slew and output loadin reality they depend onoutput slew depends on1) voltage for the particular instance as all the instances in the design will not have the same voltage2) input slew3) resistance network at the output not lumped4) capacitive network at the output no lumpedi.e. the exact rc network at the outputpropagation delay depends onsame as aboveExplain timing dependency tables of flops?same as above +input clock slewCan a cell have negative delays?a standalone cell can have. in reality you may see them.if input slew is very very slow say 10ns.logic0 at 0nslogic1 at 10nsslew measured say 0-100% of VDD is 10nsoutput slew is very fast say 1ns.logic0 at 1nslogic1 at 2nsslew measured as say 0-100% of vdd which is 2ns-1ns = 1nspropagation delay measured as 50% of input to 50% of output.50% of input is 5ns50% of output is 1.5nsthe delay is -ve 3.5this is just a silly question.How to fix timing violations?Set up timing1) check with logic designer whether it is real or non-real(such as multiple cycle or false path). If it is, add those constraints and rerun2) if it is real. Print out the violated timing path, find the cause. Depends on the design stage and the amount of violation: increase driver strength, IPO, modify floorplan to short the length of critical path interconnect, modify the RTL code, increase pipeline stage and re-synthesis.yes above and detailed info is below.to speed up a flop to flop path sayCLK->Q of first flopAND gate A->XOR gate B->X .....each gate can be faster by(1) reducing the output load (from the above timign table discussion)(2) by increasing the input slew. i.e improve the previous gate,load etc.in the above if AND gate load is reduces and gate output slew is the input slew for OR gate(3) choice of the gate looking at the timing tables (for the given input slew and output load, which has the prop. delaychoose the flop that has faster clock to q timechoose the flop that has lower setup requirementHoldGenerally hold is fixed after setup is met after route. Add delay cell. Be sure to leave some space when floor planning to insert delay cellPLACEWhat constitutes Floorplan?Die size/aspect ratio, IO placement, macro cell placement, power grid(power ring/power stripe, follow through pin)What is timing driven and congestion based placement?Both need to place the std cell in the row but the goal is different. TDD placement is to meet a certain time goal (generally a target clock frequency). Congestion based placement is to try to minimize the routing congestion to reduce DRC violations.What are rows?Area except IO, macro. The remaining area is divided into the same height row as the std cell to place std cell.Why should there be space around RAMS or IO?RAM space: create local power ring for RAMIO space : chip power ringWhat are bins and min/max ratio cut algorithms?design is usually broken in to bins or regions or windows and the placer tool chooses which cells should go into eachbin using min/max algorithm.maximize wiring inside each binminimize wiring between each bin.say bin A has 500 cells and 2000 internal wiresand bin B has 490 cells and 1900 wiresA andB has 1000 wiresmove one cell from A to B and see if the wires inside A, B are increasedand wiring between A and B is reduced. if so then move the cell to that bin.these are quiet old. i dont know what amoeba uses. but the above is the general guideline for any floorplan.you dont want too many wires between bins/regions/groups etc.you want too many wires withing one group.i.e. increase local congestiondecrease global congestion. otherwise you will never meet timing and cannot route.same way as the roads.the highway road from Dallas to Newyork is more important the local roads inside newyork and dallas.if the highway is not proper you loose more time.What are soft groups, regions and techniques of grouping?Soft groups: loosely coupled logic group. Placement tool tends to put them in closer area Region: all elements in that region must be placed in a pre-defined physical location. But other elements can also be placed in the regionWhat is scan chain reordering?After placement, reconnect the scan chain flop to minimize the routingWhat is placement-based optimization?place the std cell based on either timing constraints to meet timing goal or reducing congestion or minimizing area or combination of above.CTGENWhat is a clock tree? How does the tool know where to stop?Clock root from I/O pin or clock generator, clock sinks generally clock pin of flop and the buffer tree to connect the root and all the sinks.Stop at the clock pin of flopExplain the clock tree constraints in the given example?min, max, skew etcCan you build a clock tree through EXOR?Yes. Connect clock to one input and set the other input as a DC 1. In that case, EXOR is basically an buffer.What if Clock Tree Circuits have combinational feedback loops?Maybe oscillateCan you build trees through muxes?Yes. set the select signal always to select clock input.In multiple clock domain design, what are the problems of adverse insertion delays? setup could become impossible to meet.CLKA and CLKB have diff. insertion delays. if adverse and they both have relationship with each other (i.e. not false paths)then setup can never be met.hold will also be a huge problemROUTEWhat is routing grid?The pre-defined routing spacing for each layer of metal. Router will route the metal layer on grid onlyWhat are vias and stacked vias? Draw cross section.Via is vertical metal connecting two adjacent layers of metalStacked vias: more one layer of via directly on top of each other connecting more than 2 layers of metalHow to calculate routing grid?Check layout DRC ruleGrid = metal pitch = min metal width + min spacingWhat will happen if a pin is offgrid?Pin will not be hit or partially covered by a routing metalWhat will happen if you put standard cells below power stripes?That will block the power stripe metal layer routing access to that cell.DRCDraw the layout of an inverter?EasyWhat is manufacturing grid?Minimum manufacturing step. All layout objects must be on this gridDescribe any Design rule you can think of?Metal spacing, stack via, via spacing, poly gate encap etcWhat are process antennas?Transistor gate, source/drain connect to metal. Metal has charge. When the charge accumulates to certain amount, it will break down the gate oxide. So there is restriction on the area of metal with which a particular gate can connect.Prevention and fix: route such that not to exceed that ratio defined at DRC rule; add diode to sink the charge to ground if exceedingLVSDescribe a general LVS flow.1) stream out GDS with sub-module GDS merged2) combine sub-module transistor level netlist to obtain the top level the transistor level netlist3) obtain the golden LVS deck for the certain process4) run LVS using a physical verification tool such as Assura, Hercules or CalibreHow to get Layout and How to get the Schematic?Layout: after placement and route, merge the marco GDS, IO GDS, std cell GDS and stream out as a whole GDSSchematic: combine the sub-module transistor level netlist(provided by IP vendor) to form the top level transistor level netlistSCRIPTINGDo you know the tee command?YesDescribe any interesting unix command you know.grep, awk etcDo you know glob function in perl?No since Encounter is TCL based. Easy to learnCADENCEFlexible hours and days and work from home.Easy access to experts willing to help.Narendra’s experiencertl - netlist (synthesis - you can change a lot here)floorplan - can change a lot hereipo - still can change a lot but not more than 15% of cells. keep an eye on cell count and make sure you are still ok routingwisecksynthesis - keep an eye on buffers etc.ipo - can change but not 15% or so. it should be 5% or less. as the more you add the more you disturb clockroutesetup/drv ipo 1%hold fix 5% addedceltic bc 50 cellsceltic wc 10 cellsdoneas the design progress the more you change the more you change the clock, the routes etc.SYNOPSYSHow do control the area of your design ?First of all, there are 2 types of design: pad constraint and core constraintFor pad constraint design, the area is controlled by the IO pad. It has nothing to do with core area (enough for core)For core constraint design, after selecting IP, the parameter you can play with is area utilization. Low AU design is big but easy to minimize congestion, easy clean DRC and less coupling but high cost since low yield due to bigger areaHigh AU design is small where congestion, DRC and coupling are problems. But the yield is high 70% STD AREA UTILIZATION. CELL AREA UTILIZATION IS A GOOD NUMBER 85 AND ABOVE MIGHT CAUSE TIMINGCLOSURE/ROUTINGCLOSURE AND CELTIC CLOSURE ISSUES.LESS THAN 50 MIGHT CAUSE TIMING CLOSURE ISSUES.How do you minimize the congestion ? Especially localized congestion ?Do congestion based placement/area utilization. Better macro placement, power grid design FLOORPLAN IS THE BIGGEST KEY TO TIMING/CONGESTION/SIMOST OFTEN GOOD DESIGN CONVERGE IN ALL UNLIKE THE POPULAR BELIEF (MY PERSONAL EXPERIENCE)GOOD FLOORPLAN YIELDS TO GOOD TIMING CONGESTION NOISE ETC. YOU CANNOT MAKE ONE WORK AND NOT THE OTHER. THERE IS NO POINT IN CLOSING CONGESTION WHEN TIMING IS BAD OR VICE VERSA.YOU CAN PUT A SCREEN DENSITY (UTIL % PER AREA) ON ALL SENSITIVE AREAS TO REDUCE LOCAL CONGESTION.AGAIN REMEMBER FLOORPLAN IS THE KEY.TOOLS ALSO ARE VERY SENSITIVE TO USER CONSTRAINTS SUCH ASREGIONS/GROUPS/DENSITY AREAS. THE MORE THEY ARE THE POORER THE PERFORMANCE.IF YOU DO WANT TO CONTROL. ITS ALSO A GOOD IDEA TO PLACE CRITICAL CELLS BY HAND AND FIX THEM OR FIRST PLACE THEM THRU A TIGHT REGION CONSTRAINT. FIX THEM AND START AGAIN ONLY WITH THESE FIXED CELLS (NO MORE REGIONS) AND THEN PLACE THE REST OF THE DESIGNWhat are the three parameters associated with design ?Timing, power and costHow do you fix setup and hold violations ?Setup: speed up the logic between regs, floor plan, minimize skews, RTL code changeHold: insert delay cell and minimize skewsWhich part cannot be fixed after chip is taped out ? Setup or hold and why ?Hold since it is independent on clock frequencyHow do you find out how many flops you need during early stage of the design ? FRONTEND ALREADY DECIDES THIS. EACH ALWAYS STATEMENT IN RTL CORRESPONDS TO A FLOP.What are the physical libraries? How do you build them?LEF(size, pin location, pin layer metal, metal obstruction) used for placement and route & GDS. GDS: stream out from layoutLEF: use abstract generator to generate it from GDS/layoutLEF FOR STD CELLS AND MEMORIES COME LIBRARY VENDOR.LEF ALSO HAS A TECHNOLOGY SECTION THAT HAS ROUTING RULES (VERY CRITICAL) THAT DESCRIBES SPACING,VIA STACKING RULES ETC. THIS TECHNOLOGY SECTION IS THE ONE WE (CADENCE) OPTIMIZES FOR THE ROUTER ETC.USUALLY NOWADAYS TSMC IS GIVING DECENT TECHNOLOGY LEFS SO NO ISSUE THERE.GDS IS ALSO GIVEN BY LIBRARY VENDORBLOCK LEF SUCH AS DSP/ARM ETC THAT ARE IN YOUR DESIGN ARE GENERATED BY FE. lefOut COMMAND IF BOTTOM-UP APPROACH.IN TOPDOWN. WHEN YOU COMMIT A PARTITION THE TOOL AUTOMATICALLY GENERATES, LEF, FP TIME BUDGETED SDC ETC.What is Physical Synthesis ? How it works ?Instead relying on WLM, it takes into consideration of actual placement info to better representthe wire length to get the netlistIt needs1) RTL2) timing constraint3) floorplan info4) cell physical infoALL IPO IN FE ARE PHYSICAL SYNTHESIS.EARLIER IPO ONLY USED TO BE BUFFER INSERTION/DELETION/UPSIZE, DOWNSIZE AND SOME ADVANCED CAN DO CLONING ALSO.THE NEWER ONCE SUCH AS FE IPO ETC. HAVE ALL THE CAPABILITIES OF A SYNTHESIS ENGINE SUCH ASRESTRUCTURING, BOOLEAN OPTIMIZATION, BUFFER TREE INSERTION (LIKE CTS), MAPPING, REDUNDANCY REMOVAL, CONSTANT PROPAGATION AND EVERYTHING A SYNTHESIS CAN DO.IT DOES NOT WORK ON RTL. AS IPO DOES NOT START UNLESS THE DESIGN IS PLACED AND TO PLACE A DESIGN YOU CANNOT PLACE AN RTL DESIGN.IT NEEDS THE DESIGN FLOORPLANED AND PLACED. PHYSICAL INFO OBVIOUSLYWhat is process antenna? How do you fix them ?Transistor gate, source/drain connect to metal. Metal has charge. When the charge accumulates to certain amount, it will break down the gate oxide. So there is restriction on the area of metal with which a particular gate can connect.Prevention and fix: route such that not to exceed that ratio defined at DRC rule; add diode to sink the charge to ground if exceedingExplain how LVS work.1) stream out GDS with instances GDS merged2) combine instance transistor level netlist to obtain the top level the transistor level netlist3) obtain the golden LVS deck for the certain process4) run LVS using a physical verification tool such as Assura, Hercules or Calibre5) check report and debug(if any)(1) generate noise characterized libraries (cdb - celtic db) for all library components.read in spice of all cells and gds (no information lost as no models used)run spice simulationsand generate noise libraries.(2)for memories since spice/gds are too big to run spice simulations some approximation is done in generating cdbsRUNNING CELTIC on the design(3) generate spef with cross coupling capacitance. i.e. capacitance of each net with respect to all the nets in the vicinity.(4) run timing analysis and generate switching windows file (twf - timing windows file)(5) noise threshold set at 20% of VDD - default -(6) assume netA is at 0 and all other nets around it are switching to 1. the timing intervals and slews are obtained from twf.then, netA might see a glitch i.e. switch to 1.if the glitch is more than noise threshold (20% of VDD) then(a) propagate the glitch thru the gates and see if the glitch attenuates until it reaches a flop(b) if it reaches a flop and glitch is still present(c) does spice simulation on that flop and if Q also sees the glitch at the time, then you have a glitch viol.(7) noise on delay.assume neighboring wires are switching in the same direction(opposite for setup) as netA could have a faster transition this is recorded in the incremental sdf。

XFdtd用户手册说明书

XFdtd:Electromagnetic Simulation SoftwareElectromagnetic Simulation Solutions for Design Engineers andEM ProfessionalsRemcom provides innovative electromagnetic simulation soft ware and consulting services.Our products simplify the analysis of complex EM problems and lead the market in FDTD-based modeling and simulation.Cell phone antenna design, MRI coil analysis, antenna placement on vehicles and airplanes, and placement of wireless communication systems are made easier with Remcom’s EM simulation soft ware and expertise.Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3Powerful Flexible Modeling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4Simplifi ed Workfl ow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5Fast, Intelligent Meshing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6XACT Accurate Cell Technology. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7Results & Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8Circuit Element Optimizer (CEO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9Parameters Everywhere . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10Custom Scripted Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11High-Performance Computing Options . . . . . . . . . . . . . . . . . . . . . . . . . 12XStream GPU Acceleration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Why Use the FDTD Method? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14Specifi cations & Versions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15N T C O E N T S3Save Time and Streamline Your WorkAs an FDTD simulation solver, XFdtd outpaces other methods in effi ciency as the number of unknowns increases. Learn more on page 14.Key bene fi ts of XFdtd 3D EM Simulation Software include:•Circuit Element Optimizer determines optimal values for lumped circuit elements connected directly into the EM simulation mesh.•PrOGrid Project Optimized Gridding® simplifi es grid creation by considering multiple aspects of a project to optimize the grid for both accuracy and runtime.•XStream® GPU Acceleration for CPUs and GPU clusters enables calculations to fi nish in minutes as compared to hours. •Unlimited Memory support for problems exceeding 60 GB and billions of cells.•XACT Accurate Cell Technology® resolves the most intricate designs with fewer computational resources.•CAD Merge seamlessly integrates new versions of CAD and PCB designs into existing projects.•XTend Script Library automates modeling and design with pre-loaded, customizable scripts for creating custom features.• Guided modeling processes, editable modeling history, ability to edit imported CAD fi les.•Intelligent, ultra-fast meshing expedites previewing of fi nished meshes prior to simulation.XFdtd ®: Fast and Accurate Has Never Been So Easy4Powerful Flexible ModelingSpend less time modeling and more time gett ing results.Whether you’re importing CAD databases or building your own models, the sophisticated modeling tools in XF will make your job easier. The modeling engine in XF allows you to build complicated models from the ground up or modify imported CAD fi les. This reduces the amount of time you spend modeling, leaving you more time to focus on your results.Key Features• 2D Sketcher with constraints: Intuitive grid/objectsnapping and a constraint system allow for quick creation of complex shapes.• Feature history for objects: Modeling operations are chained together on each object,creating an editable history for each model in your project.Importable CAD Formats• ODB++• SAT/SAB • DXF• VDA-FS • STEP • IGES• Pro/E • CATIAv4• CATIAv5• Inventor •STL5Simpli fi ed Work fl owXF streamlines your workfl ow by eliminating time-consuming, redundant tasks.XF multiplies your productivity by allowing you to reuse almost anything you create. Any project can be turned into a template, the parts of your project can be stored in a shared library, and your simulations are saved and the results easily accessed for comparison purposes.Key Features• Custom project templates • Simulation history with all results • Shared libraries• Shared component, sensor, and waveformdefi nitions• PCB Merge for importing layered PCBs in ODB++• CAD MergeSeamless Revisions with CAD MergeIf you work with frequently updated CAD fi les, you’ll only have to set up the hierarchy, materialassignments and meshing priority once. XF preserves this information each time a new version of the fi le is imported, keeping your workfl ow as effi cient as possible.XF’s Assistant is a step-by-step guidethat speeds the learning curve for new users.CAD Merge compares the new geometry with the original and automatically refreshes the project treewith the changes.Run SimulationAssignMaterials,Grid, and MeshSettingsI R STI TE R AT I ON6Fast, Intelligent MeshingXF makes it easier to generate more accurate and effi cient meshes with less work.XF allows you to see the fi nished mesh with materials before the simulation ever starts. This provides the confi dence that the simulation will not fail due to a meshing error. XF’s intelligent and ultra-fast mesh updating capabilities make this process even more seamless than before.PrOGrid Project Optimized GriddingAdditionally, XF’s Project Optimized Gridding algorithm, PrOGrid, streamlines the process of generating an effi cient grid. By considering a combination of geometry features, operating frequency, and material parameters, PrOGrid intelligently creates a grid that is optimized for high accuracy and short run times.PrOGrid Logic1. Guarantee cells per wavelengthin free space and in dielectrics where the wavelength is shorter2. Reduce cell size around curvedgeometry3. Apply boundary refi nement atthe edges of conductors where electric fi elds are strongest Identify geometric features likevertices [ ] and snap grid lines to them11237XACT Accurate Cell TechnologyAccurate meshing of curved geometry.With XF, there is no need to choose performance over accuracy. XACT mesh reduces simulation time while improving the accuracy of even the most intricate designs. Using an advanced sub-cellular conformal method, XF reduces computing resources while maintaining the accuracy of a full wave solver. Faster, more accurate simulations improve the throughput of your designs from start to fi nish.Key Features• Represents small gaps and curved surfaces • Increases accuracy of results• Signifi cantly improves simulation time by reducing unknownsComparisons show the dramatic improvement with XACT.Traditional FDTD Mesh XACT MeshResults & OutputComplete result history.XF was designed to support the way you work by keeping track of every simulation youdo for each project. Results from other projects or past simulations can be added to graphs, viewed in 3D, post-processed, or exported to text fi les. The Results Browser in XF is completely customizable, and fi ltering and searching tools make it easy to fi nd exactly whatyou’re looking for with a few clicks.Approximate MR image and transmit effi ciency visual output types.Visual Output• Planes, surfaces and volumes ofoutput shown with input geometry• E/H/B, conduction current,rotating B near fi elds, in additionto dissipated power density• 3D far fi eld patt erns of E, gain,realized gain, axial ratio, radarcross section• Hearing aid compatibility, SAR,MR transmit effi ciency, andapproximate MR image outputs• Biological temperature riseGraphical Output• Near zone fi elds/currents vs. time• Impedance, S-Parameters vs.frequency, VSWR, active VSWR• Polar plot antenna patt erns• Smith chart impedance plots• FFT of transient results• Group Delay output type• Time Domain Refl ectometry (TDR)and Time Domain Transmission (TDT)output types• Dissipated Power Density9Design Flow with CEO1. Set up the XF project including copper traces,component locations, materials, grid, etc.2. Create a Response Matrix which uses FDTDsimulations to characterize fi eld interactions aff ecting the components.3. Perform a Circuit Optimization that usesS-Parameter and/or effi ciency goals to select the optimal set of component values.4. Verify that the matching network or fi lterperforms as desired with the selectedcomponent values.124Circuit Element Optimizer (CEO)Determine component values for Full-Wave Matching Circuit Optimization (FW-MCO).Circuit Element Optimization is a new technology that is only available in XF – no other electromagnetic simulation tool off ers it. It is unique because of its ability to considerelectromagnetic fi eld interactions between the components and the surrounding environment. This makes it easier than ever to fi nd the optimal set of components and achieve the desired performance with a matching network or fi lter.3S11 Threshold GPS: -6 dBBluetooth: -15 dBComponent ValuesL: 1 nH to 10 nH C: 1pF to 10 pFC1L1L20.2 pF 1.7 nH 0.6 nH10Parameters EverywhereXF helps you find the optimal solution.In XF, parameters are part of the DNA of a project. Parts, components, waveforms, materials and just about everything else in your project can leverage the power of parameters. It’s simple enough for anyone to use, but with advanced capabilities that will make any power user happy.Key Features• Defi ne nearly any value as a parameter, such as the length of a part or the frequency ofa simulation• Mathematical expressions using parameters• Interface with scripts for parameter evaluationEntire assemblies based on the same parameter can be modifi ed by changing one value. Since parameters can be used almost anywhere in XF, you can automate more things and gaincomplete control of your projects.11Custom Scripted FeaturesXF allows you to create your own custom features with a powerful scripting API.With XF, the power is in your hands to create time-saving, custom features that allow you to work faster. Nearly everything in the application can be controlled and accessed through a powerful scripting API. Whether you’re writing custom dialogs or designing custom optimization routines, the scripting API in XF breaks down the walls between what you have and what you need.Key Features• Full-featured Script Editor • Custom dialog creation through scripts• Access to Result DataThe XTend Script Library helps adapt XF to your unique processes to extend the functionality of the tool. The scripts packaged with the application are available for you to modify and fi t to your own needs. Remcom’s support team is also available to customize scripts for your specifi c use; contact Remcom for a quote.12High-Performance Computing Options for Every UserI mprove EM simulation performance using the most modern high-performance computing technologies available.Remcom’s industry-leading EM acceleration is a powerful tool to shorten your developmenttime and release your products to market sooner.Message Passing Interface (MPI) Technology for CPU and GPU ClustersDistributing XF calculations among CPU and/or GPU clusters creates limitless potential.Unlimited Memory SupportNo memory limits! Simulate massive problems exceeding billions of cells.Multiprocessor TechnologyXF calculations are parallelized across all available processors within your computer, greatly speeding calculations.ᮣ See examples and learn more at /no-limits13XStream GPU AccelerationBuilt-in EM simulation acceleration via graphics processing units.XStream tremendously improves EM simulation performance by leveraging the powerful NVIDIA graphics processing units (GPUs) available in modern video cards to make ultra-fast FDTD numerical computations. Leveraging NVIDIA’s latest generation GPUs, XStream enables XF calculations to fi nish in minutes as compared to hours or even days using a CPU only.© 2014 Remcom Inc. All rights reserved.(8 cores)Intel Xeon E5-2670(16 cores)Intel Xeon E5-2670(1)NVIDIA M2090(2)NVIDIA M2090(4)NVIDIA M2090(6)NVIDIA M2090(8)NVIDIA M2090CPUs © 2014 Remcom Inc. All rights reserved.(8)NVIDIA M2090(4)NVIDIA M2090(2)NVIDIA M2090(1)NVIDIA M2090(12)NVIDIA M2090(16)NVIDIA M2090(20)NVIDIA M2090(24)NVIDIA M2090S i m u l a t i o n T h r o u g h p u t i n G i g a c e l l s p e r S e c o n dXFdtd ® Simulation Throughput Using MPI + XStream ® GPU Acceleration51015202530Number of GPUsThroughput Plot of XStream.Throughput Plot of MPI + XStream.14Why Use the FDTD Method?While many electromagnetic simulation techniques are applied in the frequency-domain, FDTD solves Maxwell’s equations in the time domain. This means that the calculation of the electromagnetic fi eld values progresses at discrete steps in time. One benefi t of the time domain approach is that it gives broadband output from a single execution of the program; however, the main reason for using the FDTD approach is the excellent scaling performance of the method as the problem size grows. As the number of unknowns increases, the FDTD approach quickly outpaces other methods in effi ciency.FDTD has also been identifi ed as the preferred method for performing electromagnetic simulations for biological eff ects from wireless devices [1]. The FDTD method has been shown to be the most effi cient approach and provides accurate results of the fi eld penetration into biological tissues.[1] C95.3.2002, Recommended Practice for Measurements and Computations with Respect to Human Exposure to Radio Frequency Electromagnetic Fields , 100kHz to 300GHz. IEEE Standards and Coordinating Committee 28 on Non-Ionizing Radiation Hazards, April 2002.Specifi cations & Versions15© 2016 Remcom Inc. All rights reserved.NVIDIA and CUDA are trademarks and/or registered trademarks of NVIDIA Corporation in the United States and other countries.XF7.5.1.5-0216Remcom, Inc.315 S. Allen St., Suite 416State College, PA 16801 USA +1.888.7.REMCOM (US/CAN)+1.814.861.1299 phone +1.814.861.1308 fax****************Visit for more information3MBAE Systems Cobham Dynetics Ericsson GEGeneral Motors Honda HoneywellIBM LGLockheed Martin Mitsubishi Nokia Samsung Siemens SonyTexas InstrumentsToshiba ToyotaU.S. Food and Drug Administration (FDA)United States Air Force United States Army United States Marines United States Navyᮣ See /customers for more.A Sampling of Our CustomersXFdtd ®: 3D EM simulation soft ware package that provides engineers with powerful and innovative tools for modeling and EM soft ware simulation.Wireless InSite ®: A radiopropagation analysis package for analyzing the impact of the physical environment on the performance of wireless communication systems.XGtd ®: A high frequency GTD/UTD based package for the design and analysis of antenna systems on complex objects such as vehicles and aircraft .Remcom has been leading the EM market with innovative simulation and wireless propagation tools for more than 20 years. Our family of products includes:。

ganhemt器件建模与高效率功率放大器研究

摘要微波功率放大器是无线通信系统的核心器件,随着通信系统的小型化、可靠性等需求进一步提高,高效率功率放大器成为新一代无线通信系统的瓶颈。

近年来,氮化镓(GaN)高电子迁移率晶体管(HEMT)以高频、高功率、高效率、耐高温等优势,成为国内外固态功率器件研究的热点。

大信号器件模型是电路优化设计的前提,在优化器件结构、提高功率放大器电路性能等方面具有重要意义。

因此,本文从模型出发,针对高效率功率放大器设计理论与方法进行了研究,主要内容包括:(1)Pi型网络E类功率放大器的理论研究。

针对微波晶体管输出寄生电感,导致传统E类功率放大器工作频率、带宽受限等问题,提出了pi型网络E类功率放大器拓扑。

推导出了该拓扑电流电压的解析表达式,给出了在最大负载、最大工作频率、并联谐振、二次谐波并联谐振等特殊情况下的波形,计算出了在宽带范围内的电流电压最大值和输出功率能力,并给出了pi型网络E类功率放大器负载网络的归一化元件值解析公式。

结果表明,pi型网络E类功率放大器相比传统拓扑结构具有设计灵活、输出功率能力高等优势,为提高功率放大器性能提供了参考。

(2)宽带pi型网络E类功率放大器研究。

针对pi型网络E类功率放大器设计理论与方法,研究了晶体管输出寄生串联电感对负载电阻、串联电抗、最大工作频率、负载电流初始相位的影响。

分析结果表明,优化输出串联电感值可以增加负载网络的带宽。

进一步分析了输出串联电感对负载网络的电导、电纳、负载的相位的变化规律,利用自建的微波GaN HEMT大信号等效电路模型,设计制作了S波段 pi型网络E类功率放大器,在2.5~3.5GHz(33.3%相对带宽)下,漏极效率为60%~69%,输出功率大于35.2dBm,拓宽了工作频率,且在高频宽带下,实现了高效率功放。

(3)宽带pi型网络EF3类功率放大器研究。

为进一步提高效率,在pi型网络E类功率放大器具有宽带特性的基础上,基于EF类功率放大器的原理,提出了一种pi型网络EF3类功率放大器。

AAnalyst800原子吸收光谱仪操作说明书[1]

![AAnalyst800原子吸收光谱仪操作说明书[1]](https://img.taocdn.com/s3/m/3bed74856bec0975f465e2c5.png)

分析前准备工作开机装灯关机开机1.操作前仔细阅读安全须知。

2.确证分光光度计及其他辅助仪器安装正确。

3.打开工作区排风系统。

4.接通空气压缩机电源,空气过滤器减压至约450KPa。

打开乙炔钢瓶(调节为90KPa)5. 打开惰性气体钢瓶并调节为350KPa。

6.接通冷却水i 如用循环冷却水系统,按揿其后板上开关ii 如用自来水冷却,流速调节为2.5升/分7.将主机后板上空气开关( circuit breaker)拨向ON的位置(记号为1)可将此开关一直在ON的位置上,而开机时用面板上ON/OFF开关8.接通计算机9.装灯(开机前必须已有一只空心阴极灯在灯架上)10.打开面板上ON/OFF开关(待空压机达到额定压力后,再开主机)11.开动AA Winlab,在AA Winlab图块上双击12.选择原子化器*如果需要的原子化器不在原子化器室内,则按以下步骤进行i确信石墨炉自动进样器已从原子化器室前旋转至旁边位置,雾化器管子没有接任何附件ⅱ确信空压机已接通ⅲ在File菜单上Change Technique单击ⅳ选择所需原子化器Flame—燃烧器系统Furnace—石墨炉ⅴ在OK上单击,显示Initializing New Technique注:在原子化器转变时,切勿将手或其他物品放在原子化器室内I. 装灯灯室位于分光光度计左侧有八个灯架空心阴极灯可以装在任何一个灯架上如装无极灯,则只能装在灯架1-4上无极灯插座在灯室左侧灯室内灯架II. 灯的安装和连接A. 空心阴极灯HCL注: 开机前必须已有一只空心阴极灯在灯架上1.打开灯室2.将Lumina灯小心地滑进灯架插头要全部滑进灯架上插座3.关上灯室盖子B. 无极放电灯EDL只能用灯架1-41.打开灯室1.将灯驱动器滑进套筒,当套筒滑入时,压住锁住栓,到位后,锁住栓会伸出套筒孔。

1.将灯滑进灯架,直至撞上灯架内的终止点。

1.将编码灯插头插入灯架上插座(灯架与插座须同号)。

基于关键路径与改进遗传算法的最佳占空比求解

基于关键路径与改进遗传算法的最佳占空比求解徐辉;李丹青;应健锋;李扬【摘要】纳米工艺下,负偏置温度不稳定性(NBTI)成为影响电路老化效应的主导因素.多输入向量控制(M-IVC)是缓解由于NBTI效应引起电路老化的有效方法,而M-IVC的关键是最佳占空比的求解.在充分考虑时序余量的设计与电路实际操作情况下,对电路采用了静态时序分析,精确定位电路中关键路径.对关键路径采用改进的自适应遗传算法求解最佳占空比.实验结果表明:在时序余量为5%时,电路的平均老化率相比现有方案降低了1.49%,平均相对改善率为18.29%.%Under the nanometer process,the negative bias temperature instability (NBTI) is the dominant factor affecting the aging effect of the circuit. Multi input vector control (M-IVC) is an effective method to mitigate the NBTI effect,and the key to M-IVC is the solution of the optimal duty cycle. After fully considering the original design of the time margin and the actual operation of the circuit,the static timing analysis is used to accurately locate the critical path in the circuit. The improved adaptive genetic algorithm is used to solve the critical path for the best duty cycle. The experimental results show that when the time margin is 5%,the average aging rate of the circuit is reduced by 1. 49% compared with the existing scheme,and the average relative improvement rate is 18. 29%.【期刊名称】《传感器与微系统》【年(卷),期】2017(036)010【总页数】5页(P124-128)【关键词】集成电路;老化效应;最佳占空比;负偏置温度不稳定性;多输入向量控制;遗传算法【作者】徐辉;李丹青;应健锋;李扬【作者单位】安徽理工大学计算机科学与工程学院,安徽淮南232001;安徽理工大学计算机科学与工程学院,安徽淮南232001;合肥工业大学电子科学与应用物理学院,安徽合肥230009;江苏商贸职业学院信息系,江苏南通226011【正文语种】中文【中图分类】TN407应集成电路的发展需求,晶体管的特征尺寸不断按比例缩放,使得负偏置温度不稳定性(negative bias temperature instability,NBTI)成为引起电路老化的主导因素[1]。

英语作文-集成电路设计中的优化算法与设计方法解析

英语作文-集成电路设计中的优化算法与设计方法解析In the field of integrated circuit design, optimization algorithms and design methods play a crucial role in improving the performance and efficiency of circuits. These algorithms and methods aim to minimize power consumption, maximize speed, and enhance reliability. In this article, we will analyze the various optimization algorithms and design methods used in integrated circuit design.One commonly used optimization algorithm in integrated circuit design is the Genetic Algorithm (GA). GA is inspired by the process of natural selection and evolution. It starts with an initial population of potential solutions and applies genetic operators such as selection, crossover, and mutation to generate new solutions. Through successive generations, the algorithm converges towards the optimal solution. GA has been successfully applied in various aspects of integrated circuit design, including floorplanning, placement, routing, and logic synthesis.Another widely used optimization algorithm is the Simulated Annealing (SA) algorithm. SA is based on the annealing process of cooling and slowly heating a material to reduce defects and improve its properties. In the context of integrated circuit design, SA starts with an initial solution and iteratively explores the solution space by accepting worse solutions with a certain probability. This allows the algorithm to escape local optima and converge towards a global optimum. SA has been applied to problems such as placement, routing, and timing optimization in integrated circuit design.In addition to optimization algorithms, design methods also play a crucial role in integrated circuit design. One commonly used design method is the Register-Transfer Level (RTL) design. RTL design focuses on capturing the behavior of a circuit using a hardware description language such as Verilog or VHDL. It allows designers to specify the functionality of the circuit at a higher level of abstraction before the actualimplementation. RTL design enables efficient circuit exploration and optimization before the physical design stage.Another important design method is High-Level Synthesis (HLS). HLS allows designers to describe the circuit's behavior using a high-level programming language such as C or C++. The HLS tool then automatically generates the corresponding hardware implementation. This design method enables designers to explore different architectural optimizations and trade-offs at a higher level of abstraction. HLS has been widely used in the design of digital signal processing circuits and complex system-on-chip designs.Furthermore, in the era of deep learning and artificial intelligence, optimization algorithms and design methods have also been applied to the design of specialized hardware for accelerating neural networks. Techniques such as neural architecture search, quantization, and pruning have been developed to optimize the performance and energy efficiency of neural network accelerators.In conclusion, optimization algorithms and design methods are essential in integrated circuit design. They enable designers to improve the performance, efficiency, and reliability of circuits. Genetic algorithms, simulated annealing, RTL design, and high-level synthesis are just a few examples of the many techniques used in integrated circuit design. As technology advances, new algorithms and methods will continue to emerge, pushing the boundaries of integrated circuit design further.。

cad_flows

BR 6/00

11

Formal Verification Categories

• Equivalence Checking – most widely used, easiest

– Use a mathematical approach to compare a reference design to a revised design (do two netlists implement the same boolean function?) – Reference design must be correct

IPO/Physical Hierarchy

Hale Waihona Puke BR 6/003“Timing Closure”

• “Timing Closure” refers to producing a design that meets timing specifications

– Want to verify that your design has timing closure before you fabricate

BR 6/00 10

Formal Verification

• Formal Verification means that mathematical techniques to prove that the hardware is correct as it progresses from one abstraction level to another (Behavioral to RTL to Gatelevel to Physical), etc. • Attraction is that circuit does not have to be simulated – no need for test vector generation

单分子综述-NATURE NANOTECHNOLOGY-Single-molecule junctions beyond electronic transport-2013

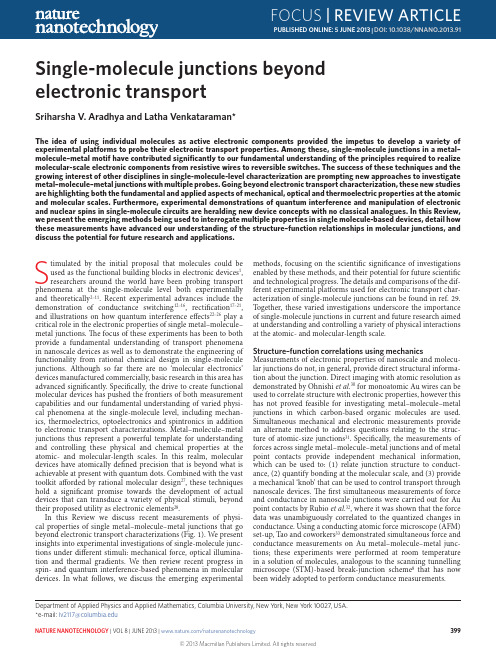

Stimulated by the initial proposal that molecules could be used as the functional building blocks in electronic devices 1, researchers around the world have been probing transport phenomena at the single-molecule level both experimentally and theoretically 2–11. Recent experimental advances include the demonstration of conductance switching 12–16, rectification 17–21, and illustrations on how quantum interference effects 22–26 play a critical role in the electronic properties of single metal–molecule–metal junctions. The focus of these experiments has been to both provide a fundamental understanding of transport phenomena in nanoscale devices as well as to demonstrate the engineering of functionality from rational chemical design in single-molecule junctions. Although so far there are no ‘molecular electronics’ devices manufactured commercially, basic research in this area has advanced significantly. Specifically, the drive to create functional molecular devices has pushed the frontiers of both measurement capabilities and our fundamental understanding of varied physi-cal phenomena at the single-molecule level, including mechan-ics, thermoelectrics, optoelectronics and spintronics in addition to electronic transport characterizations. Metal–molecule–metal junctions thus represent a powerful template for understanding and controlling these physical and chemical properties at the atomic- and molecular-length scales. I n this realm, molecular devices have atomically defined precision that is beyond what is achievable at present with quantum dots. Combined with the vast toolkit afforded by rational molecular design 27, these techniques hold a significant promise towards the development of actual devices that can transduce a variety of physical stimuli, beyond their proposed utility as electronic elements 28.n this Review we discuss recent measurements of physi-cal properties of single metal–molecule–metal junctions that go beyond electronic transport characterizations (Fig. 1). We present insights into experimental investigations of single-molecule junc-tions under different stimuli: mechanical force, optical illumina-tion and thermal gradients. We then review recent progress in spin- and quantum interference-based phenomena in molecular devices. I n what follows, we discuss the emerging experimentalSingle-molecule junctions beyond electronic transportSriharsha V. Aradhya and Latha Venkataraman*The id ea of using ind ivid ual molecules as active electronic components provid ed the impetus to d evelop a variety of experimental platforms to probe their electronic transport properties. Among these, single-molecule junctions in a metal–molecule–metal motif have contributed significantly to our fundamental understanding of the principles required to realize molecular-scale electronic components from resistive wires to reversible switches. The success of these techniques and the growing interest of other disciplines in single-molecule-level characterization are prompting new approaches to investigate metal–molecule–metal junctions with multiple probes. Going beyond electronic transport characterization, these new studies are highlighting both the fundamental and applied aspects of mechanical, optical and thermoelectric properties at the atomic and molecular scales. Furthermore, experimental demonstrations of quantum interference and manipulation of electronic and nuclear spins in single-molecule circuits are heralding new device concepts with no classical analogues. In this Review, we present the emerging methods being used to interrogate multiple properties in single molecule-based devices, detail how these measurements have advanced our understanding of the structure–function relationships in molecular junctions, and discuss the potential for future research and applications.methods, focusing on the scientific significance of investigations enabled by these methods, and their potential for future scientific and technological progress. The details and comparisons of the dif-ferent experimental platforms used for electronic transport char-acterization of single-molecule junctions can be found in ref. 29. Together, these varied investigations underscore the importance of single-molecule junctions in current and future research aimed at understanding and controlling a variety of physical interactions at the atomic- and molecular-length scale.Structure–function correlations using mechanicsMeasurements of electronic properties of nanoscale and molecu-lar junctions do not, in general, provide direct structural informa-tion about the junction. Direct imaging with atomic resolution as demonstrated by Ohnishi et al.30 for monoatomic Au wires can be used to correlate structure with electronic properties, however this has not proved feasible for investigating metal–molecule–metal junctions in which carbon-based organic molecules are used. Simultaneous mechanical and electronic measurements provide an alternate method to address questions relating to the struc-ture of atomic-size junctions 31. Specifically, the measurements of forces across single metal–molecule–metal junctions and of metal point contacts provide independent mechanical information, which can be used to: (1) relate junction structure to conduct-ance, (2) quantify bonding at the molecular scale, and (3) provide a mechanical ‘knob’ that can be used to control transport through nanoscale devices. The first simultaneous measurements of force and conductance in nanoscale junctions were carried out for Au point contacts by Rubio et al.32, where it was shown that the force data was unambiguously correlated to the quantized changes in conductance. Using a conducting atomic force microscope (AFM) set-up, Tao and coworkers 33 demonstrated simultaneous force and conductance measurements on Au metal–molecule–metal junc-tions; these experiments were performed at room temperature in a solution of molecules, analogous to the scanning tunnelling microscope (STM)-based break-junction scheme 8 that has now been widely adopted to perform conductance measurements.Department of Applied Physics and Applied Mathematics, Columbia University, New York, New York 10027, USA. *e-mail: lv2117@DOI: 10.1038/NNANO.2013.91These initial experiments relied on the so-called static mode of AFM-based force spectroscopy, where the force on the canti-lever is monitored as a function of junction elongation. I n this method the deflection of the AFM cantilever is directly related to the force on the junction by Hooke’s law (force = cantilever stiff-ness × cantilever deflection). Concurrently, advances in dynamic force spectroscopy — particularly the introduction of the ‘q-Plus’ configuration 34 that utilizes a very stiff tuning fork as a force sen-sor — are enabling high-resolution measurements of atomic-size junctions. In this technique, the frequency shift of an AFM cantilever under forced near-resonance oscillation is measuredas a function of junction elongation. This frequency shift can be related to the gradient of the tip–sample force. The underlying advantage of this approach is that frequency-domain measure-ments of high-Q resonators is significantly easier to carry out with high precision. However, in contrast to the static mode, recover-ing the junction force from frequency shifts — especially in the presence of dissipation and dynamic structural changes during junction elongation experiments — is non-trivial and a detailed understanding remains to be developed 35.The most basic information that can be determined throughsimultaneous measurement of force and conductance in metalThermoelectricsSpintronics andMechanicsOptoelectronicsHotColdFigure 1 | Probing multiple properties of single-molecule junctions. phenomena in addition to demonstrations of quantum mechanical spin- and interference-dependent transport concepts for which there are no analogues in conventional electronics.contacts is the relation between the measured current and force. An experimental study by Ternes et al.36 attempted to resolve a long-standing theoretical prediction 37 that indicated that both the tunnelling current and force between two atomic-scale metal contacts scale similarly with distance (recently revisited by Jelinek et al.38). Using the dynamic force microscopy technique, Ternes et al. effectively probed the interplay between short-range forces and conductance under ultrahigh-vacuum conditions at liquid helium temperatures. As illustrated in Fig. 2a, the tunnel-ling current through the gap between the metallic AFM probe and the substrate, and the force on the cantilever were recorded, and both were found to decay exponentially with increasing distance with nearly the same decay constant. Although an exponential decay in current with distance is easily explained by considering an orbital overlap of the tip and sample wavefunctions through a tunnel barrier using Simmons’ model 39, the exponential decay in the short-range forces indicated that perhaps the same orbital controlled the interatomic short-range forces (Fig. 2b).Using such dynamic force microscopy techniques, research-ers have also studied, under ultrahigh-vacuum conditions, forces and conductance across junctions with diatomic adsorbates such as CO (refs 40,41) and more recently with fullerenes 42, address-ing the interplay between electronic transport, binding ener-getics and structural evolution. I n one such experiment, Tautz and coworkers 43 have demonstrated simultaneous conduct-ance and stiffness measurements during the lifting of a PTCDA (3,4,9,10-perylene-tetracarboxylicacid-dianhydride) molecule from a Ag(111) substrate using the dynamic mode method with an Ag-covered tungsten AFM tip. The authors were able to follow the lifting process (Fig. 2c,d) monitoring the junction stiffness as the molecule was peeled off the surface to yield a vertically bound molecule, which could also be characterized electronically to determine the conductance through the vertical metal–molecule–metal junction with an idealized geometry. These measurements were supported by force field-based model calculations (Fig. 2c and dashed black line in Fig. 2d), presenting a way to correlate local geometry to the electronic transport.Extending the work from metal point contacts, ambient meas-urements of force and conductance across single-molecule junc-tions have been carried out using the static AFM mode 33. These measurements allow correlation of the bond rupture forces with the chemistry of the linker group and molecular backbone. Single-molecule junctions are formed between a Au-metal sub-strate and a Au-coated cantilever in an environment of molecules. Measurements of current through the junction under an applied bias determine conductance, while simultaneous measurements of cantilever deflection relate to the force applied across the junction as shown in Fig. 2e. Although measurements of current throughzF zyxCantileverIVabConductance G (G 0)1 2 3Tip–sample distance d (Å)S h o r t -r a n g e f o r c e F z (n N )10−310−210−11110−110−210−3e10−410−210C o n d u c t a n c e (G 0)Displacement86420Force (nN)0.5 nm420−2F o r c e (n N )−0.4−0.200.20.4Displacement (nm)SSfIncreasing rupture forcegc(iv)(i)(iii)(ii)Low HighCounts d9630−3d F /d z (n N n m −1)(i)(iv)(iii)(ii)A p p r o a chL i ft i n g110−210−4G (2e 2/h )2051510z (Å)H 2NNH 2H 2NNH 2NNFigure 2 | Simultaneous measurements of electronic transport and mechanics. a , A conducting AFM set-up with a stiff probe (shown schematically) enabled the atomic-resolution imaging of a Pt adsorbate on a Pt(111) surface (tan colour topography), before the simultaneous measurement of interatomic forces and currents. F z , short-range force. b , Semilogarithmic plot of tunnelling conductance and F z measured over the Pt atom. A similar decay constant for current and force as a function of interatomic distance is seen. The blue dashed lines are exponential fits to the data. c , Structural snapshots showing a molecular mechanics simulation of a PTCDA molecule held between a Ag substrate and tip (read right to left). It shows the evolution of the Ag–PTCDA–Ag molecular junction as a function of tip–surface distance. d , Upper panel shows experimental stiffness (d F /d z ) measurements during the lifting process performed with a conducting AFM. The calculated values from the simulation are overlaid (dashed black line). Lower panel shows simultaneously measured conductance (G ). e , Simultaneously measured conductance (red) and force (blue) measurements showing evolution of a molecular junction as a function of junction elongation. A Au point contact is first formed, followed by the formation of a single-molecule junction, which then ruptures on further elongation. f , A two-dimensional histogram of thousands of single-molecule junctionrupture events (for 1,4-bis(methyl sulphide) butane; inset), constructed by redefining the rupture location as the zero displacement point. The most frequently measured rupture force is the drop in force (shown by the double-headed arrow) at the rupture location in the statistically averaged force trace (overlaid black curve). g , Beyond the expected dependence on the terminal group, the rupture force is also sensitive to the molecular backbone, highlighting the interplay between chemical structure and mechanics. In the case of nitrogen-terminated molecules, rupture force increases fromaromatic amines to aliphatic amines and the highest rupture force is for molecules with pyridyl moieties. Figure reproduced with permission from: a ,b , ref. 36, © 2011 APS; c ,d , ref. 43, © 2011 APS.DOI: 10.1038/NNANO.2013.91such junctions are easily accomplished using standard instru-mentation, measurements of forces with high resolution are not straightforward. This is because a rather stiff cantilever (with a typical spring constant of ~50 N m−1) is typically required to break the Au point contact that is first formed between the tip and sub-strate, before the molecular junctions are created. The force reso-lution is then limited by the smallest deflection of the cantilever that can be measured. With a custom-designed system24 our group has achieved a cantilever displacement resolution of ~2 pm (com-pare with Au atomic diameter of ~280 pm) using an optical detec-tion scheme, allowing the force noise floor of the AFM set-up to be as low as 0.1 nN even with these stiff cantilevers (Fig. 2e). With this system, and a novel analysis technique using two-dimensional force–displacement histograms as illustrated in Fig. 2f, we have been able to systematically probe the influence of the chemical linker group44,45 and the molecular backbone46 on single-molecule junction rupture force as illustrated in Fig. 2g.Significant future opportunities with force measurements exist for investigations that go beyond characterizations of the junc-tion rupture force. In two independent reports, one by our group47 and another by Wagner et al.48, force measurements were used to quantitatively measure the contribution of van der Waals interac-tions at the single-molecule level. Wagner et al. used the stiffness data from the lifting of PTCDA molecules on a Au(111) surface, and fitted it to the stiffness calculated from model potentials to estimate the contribution of the various interactions between the molecule and the surface48. By measuring force and conductance across single 4,4’-bipyridine molecules attached to Au electrodes, we were able to directly quantify the contribution of van der Waals interactions to single-molecule-junction stiffness and rupture force47. These experimental measurements can help benchmark the several theoretical frameworks currently under development aiming to reliably capture van der Waals interactions at metal/ organic interfaces due to their importance in diverse areas includ-ing catalysis, electronic devices and self-assembly.In most of the experiments mentioned thus far, the measured forces were typically used as a secondary probe of junction prop-erties, instead relying on the junction conductance as the primary signature for the formation of the junction. However, as is the case in large biological molecules49, forces measured across single-mol-ecule junctions can also provide the primary signature, thereby making it possible to characterize non-conducting molecules that nonetheless do form junctions. Furthermore, molecules pos-sess many internal degrees of motion (including vibrations and rotations) that can directly influence the electronic transport50, and the measurement of forces with such molecules can open up new avenues for mechanochemistry51. This potential of using force measurements to elucidate the fundamentals of electronic transport and binding interactions at the single-molecule level is prompting new activity in this area of research52–54. Optoelectronics and optical spectroscopyAddressing optical properties and understanding their influence on electronic transport in individual molecular-scale devices, col-lectively referred to as ‘molecular optoelectronics’, is an area with potentially important applications55. However, the fundamental mismatch between the optical (typically, approximately at the micrometre scale) and molecular-length scales has historically presented a barrier to experimental investigations. The motiva-tions for single-molecule optoelectronic studies are twofold: first, optical spectroscopies (especially Raman spectroscopy) could lead to a significantly better characterization of the local junction structure. The nanostructured metallic electrodes used to real-ize single-molecule junctions are coincidentally some of the best candidates for local field enhancement due to plasmons (coupled excitations of surface electrons and incident photons). This there-fore provides an excellent opportunity for understanding the interaction of plasmons with molecules at the nanoscale. Second, controlling the electronic transport properties using light as an external stimulus has long been sought as an attractive alternative to a molecular-scale field-effect transistor.Two independent groups have recently demonstrated simulta-neous optical and electrical measurements on molecular junctions with the aim of providing structural information using an optical probe. First, Ward et al.56 used Au nanogaps formed by electromi-gration57 to create molecular junctions with a few molecules. They then irradiated these junctions with a laser operating at a wavelength that is close to the plasmon resonance of these Au nanogaps to observe a Raman signal attributable to the molecules58 (Fig. 3a). As shown in Fig. 3b, they observed correlations between the intensity of the Raman features and magnitude of the junction conductance, providing direct evidence that Raman signatures could be used to identify junction structures. They later extended this experimental approach to estimate vibrational and electronic heating in molecu-lar junctions59. For this work, they measured the ratio of the Raman Stokes and anti-Stokes intensities, which were then related to the junction temperature as a function of the applied bias voltage. They found that the anti-Stokes intensity changed with bias voltage while the Stokes intensity remained constant, indicating that the effective temperature of the Raman-active mode was affected by passing cur-rent through the junction60. Interestingly, Ward et al. found that the vibrational mode temperatures exceeded several hundred kelvin, whereas earlier work by Tao and co-workers, who used models for junction rupture derived from biomolecule research, had indicated a much smaller value (~10 K) for electronic heating61. Whether this high temperature determined from the ratio of the anti-Stokes to Stokes intensities indicates that the electronic temperature is also similarly elevated is still being debated55, however, one can definitely conclude that such measurements under a high bias (few hundred millivolts) are clearly in a non-equilibrium transport regime, and much more research needs to be performed to understand the details of electronic heating.Concurrently, Liu et al.62 used the STM-based break-junction technique8 and combined this with Raman spectroscopy to per-form simultaneous conductance and Raman measurements on single-molecule junctions formed between a Au STM tip and a Au(111) substrate. They coupled a laser to a molecular junction as shown in Fig. 3c with a 4,4’-bipyridine molecule bridging the STM tip (top) and the substrate (bottom). Pyridines show clear surface-enhanced Raman signatures on metal58, and 4,4’-bipy-ridine is known to form single-molecule junctions in the STM break-junction set-up8,15. Similar to the study of Ward et al.56, Liu et al.62 found that conducting molecular junctions had a Raman signature that was distinct from the broken molecu-lar junctions. Furthermore, the authors studied the spectra of 4,4’-bipyridine at different bias voltages, ranging from 10 to 800 mV, and reported a reversible splitting of the 1,609 cm–1 peak (Fig. 3d). Because this Raman signature is due to a ring-stretching mode, they interpreted this splitting as arising from the break-ing of the degeneracy between the rings connected to the source and drain electrodes at high biases (Fig. 3c). Innovative experi-ments such as these have demonstrated that there is new physics to be learned through optical probing of molecular junctions, and are initiating further interest in understanding the effect of local structure and vibrational effects on electronic transport63. Experiments that probe electroluminescence — photon emis-sion induced by a tunnelling current — in these types of molec-ular junction can also offer insight into structure–conductance correlations. Ho and co-workers have demonstrated simultaneous measurement of differential conductance and photon emissionDOI: 10.1038/NNANO.2013.91from individual molecules at a submolecular-length scale using an STM 64,65. Instead of depositing molecules directly on a metal sur-face, they used an insulating layer to decouple the molecule from the metal 64,65 (Fig. 3e). This critical factor, combined with the vac-uum gap with the STM tip, ensures that the metal electrodes do not quench the radiated photons, and therefore the emitted photons carry molecular fingerprints. Indeed, the experimental observation of molecular electroluminescence of C 60 monolayers on Au(110) by Berndt et al.66 was later attributed to plasmon-mediated emission of the metallic electrodes, indirectly modulated by the molecule 67. The challenge of finding the correct insulator–molecule combination and performing the experiments at low temperature makes electro-luminescence relatively uncommon compared with the numerous Raman studies; however, progress is being made on both theoretical and experimental fronts to understand and exploit emission pro-cesses in single-molecule junctions 68.Beyond measurements of the Raman spectra of molecular junctions, light could be used to control transport in junctions formed with photochromic molecular backbones that occur in two (or more) stable and optically accessible states. Some common examples include azobenzene derivatives, which occur in a cis or trans form, as well as diarylene compounds that can be switched between a conducting conjugated form and a non-conducting cross-conjugated form 69. Experiments probing the conductance changes in molecular devices formed with such compounds have been reviewed in depth elsewhere 70,71. However, in the single-mol-ecule context, there are relatively few examples of optical modula-tion of conductance. To a large extent, this is due to the fact that although many molecular systems are known to switch reliably in solution, contact to metallic electrodes can dramatically alter switching properties, presenting a significant challenge to experi-ments at the single-molecule level.Two recent experiments have attempted to overcome this chal-lenge and have probed conductance changes in single-molecule junctions while simultaneously illuminating the junctions with visible light 72,73. Battacharyya et al.72 used a porphyrin-C 60 ‘dyad’ molecule deposited on an indium tin oxide (I TO) substrate to demonstrate the light-induced creation of an excited-state mol-ecule with a different conductance. The unconventional transpar-ent ITO electrode was chosen to provide optical access while also acting as a conducting electrode. The porphyrin segment of the molecule was the chromophore, whereas the C 60 segment served as the electron acceptor. The authors found, surprisingly, that the charge-separated molecule had a much longer lifetime on ITO than in solution. I n the break-junction experiments, the illuminated junctions showed a conductance feature that was absent without1 μm Raman shift (cm –1)1,609 cm –1(–)Source 1,609 cm–1Drain (+)Low voltage High voltageMgPNiAl(110)STM tip (Ag)VacuumThin alumina 1.4 1.5 1.6 1.701020 3040200400Photon energy (eV)3.00 V 2.90 V 2.80 V 2.70 V 2.60 V2.55 V 2.50 VP h o t o n c o u n t s (a .u .)888 829 777731Wavelength (nm)Oxideacebd f Raman intensity (CCD counts)1,5001,00050000.40.30.20.10.01,590 cm −11,498 cm −1d I /d V (μA V –1)1,609 cm –11,631 cm–11 μm1 μmTime (s)Figure 3 | Simultaneous studies of optical effects and transport. a , A scanning electron micrograph (left) of an electromigrated Au junction (light contrast) lithographically defined on a Si substrate (darker contrast). The nanoscale gap results in a ‘hot spot’ where Raman signals are enhanced, as seen in the optical image (right). b , Simultaneously measured differential conductance (black, bottom) and amplitudes of two molecular Raman features (blue traces, middle and top) as a function of time in a p-mercaptoaniline junction. c , Schematic representation of a bipyridine junction formed between a Au STM tip and a Au(111) substrate, where the tip enhancement from the atomically sharp STM tip results in a large enhancement of the Raman signal. d , The measured Raman spectra as a function of applied bias indicate breaking of symmetry in the bound molecule. e , Schematic representation of a Mg-porphyrin (MgP) molecule sandwiched between a Ag STM tip and a NiAl(110) substrate. A subnanometre alumina insulating layer is a key factor in measuring the molecular electroluminescence, which would otherwise be overshadowed by the metallic substrate. f , Emission spectra of a single Mg-porphyrin molecule as a function of bias voltage (data is vertically offset for clarity). At high biases, individual vibronic peaks become apparent. The spectra from a bare oxide layer (grey) is shown for reference. Figure reproduced with permission from: a ,b , ref. 56, © 2008 ACS; c ,d , ref. 62, © 2011 NPG; e ,f , ref. 65, © 2008 APS.DOI: 10.1038/NNANO.2013.91light, which the authors assigned to the charge-separated state. In another approach, Lara-Avila et al.73 have reported investigations of a dihydroazulene (DHA)/vinylheptafulvene (VHF) molecule switch, utilizing nanofabricated gaps to perform measurements of Au–DHA–Au single-molecule junctions. Based on the early work by Daub et al.74, DHA was known to switch to VHF under illumina-tion by 353-nm light and switch back to DHA thermally. In three of four devices, the authors observed a conductance increase after irradiating for a period of 10–20 min. In one of those three devices, they also reported reversible switching after a few hours. Although much more detailed studies are needed to establish the reliability of optical single-molecule switches, these experiments provide new platforms to perform in situ investigations of single-molecule con-ductance under illumination.We conclude this section by briefly pointing to the rapid pro-gress occurring in the development of optical probes at the single-molecule scale, which is also motivated by the tremendous interest in plasmonics and nano-optics. As mentioned previously, light can be coupled into nanoscale gaps, overcoming experimental chal-lenges such as local heating. Banerjee et al.75 have exploited these concepts to demonstrate plasmon-induced electrical conduction in a network of Au nanoparticles that form metal–molecule–metal junctions between them (Fig. 3f). Although not a single-molecule measurement, the control of molecular conductance through plas-monic coupling can benefit tremendously from the diverse set of new concepts under development in this area, such as nanofabri-cated transmission lines 76, adiabatic focusing of surface plasmons, electrical excitation of surface plasmons and nanoparticle optical antennas. The convergence of plasmonics and electronics at the fundamental atomic- and molecular-length scales can be expected to provide significant opportunities for new studies of light–mat-ter interaction 77–79.Thermoelectric characterization of single-molecule junctions Understanding the electronic response to heating in a single-mole-cule junction is not only of basic scientific interest; it can have a tech-nological impact by improving our ability to convert wasted heat into usable electricity through the thermoelectric effect, where a temper-ature difference between two sides of a device induces a voltage drop across it. The efficiency of such a device depends on its thermopower (S ; also known as the Seebeck coefficient), its electric and thermal conductivity 80. Strategies for increasing the efficiency of thermoelec-tric devices turned to nanoscale devices a decade ago 81, where one could, in principle, increase the electronic conductivity and ther-mopower while independently minimizing the thermal conductiv-ity 82. This has motivated the need for a fundamental understandingof thermoelectrics at the single-molecule level 83, and in particular, the measurement of the Seebeck coefficient in such junctions. The Seebeck coefficient, S = −(ΔV /ΔT )|I = 0, determines the magnitude of the voltage developed across the junction when a temperature dif-ference ΔT is applied, as illustrated in Fig. 4a; this definition holds both for bulk devices and for single-molecule junctions. If an addi-tional external voltage ΔV exists across the junction, then the cur-rent I through the junction is given by I = G ΔV + GS ΔT where G is the junction conductance 83. Transport through molecular junctions is typically in the coherent regime where conductance, which is pro-portional to the electronic transmission probability, is given by the Landauer formula 84. The Seebeck coefficient at zero applied voltage is then related to the derivative of the transmission probability at the metal Fermi energy (in the off-resonance limit), with, S = −∂E ∂ln( (E ))π2k 2B T E 3ewhere k B is the Boltzmann constant, e is the charge of the electron, T (E ) is the energy-dependent transmission function and E F is the Fermi energy. When the transmission function for the junction takes on a simple Lorentzian form 85, and transport is in the off-resonance limit, the sign of S can be used to deduce the nature of charge carriers in molecular junctions. In such cases, a positive S results from hole transport through the highest occupied molecu-lar orbital (HOMO) whereas a negative S indicates electron trans-port through the lowest unoccupied molecular orbital (LUMO). Much work has been performed on investigating the low-bias con-ductance of molecular junctions using a variety of chemical linker groups 86–89, which, in principle, can change the nature of charge carriers through the junction. Molecular junction thermopower measurements can thus be used to determine the nature of charge carriers, correlating the backbone and linker chemistry with elec-tronic aspects of conduction.Experimental measurements of S and conductance were first reported by Ludoph and Ruitenbeek 90 in Au point contacts at liquid helium temperatures. This work provided a method to carry out thermoelectric measurements on molecular junctions. Reddy et al.91 implemented a similar technique in the STM geome-try to measure S of molecular junctions, although due to electronic limitations, they could not simultaneously measure conductance. They used thiol-terminated oligophenyls with 1-3-benzene units and found a positive S that increased with increasing molecular length (Fig. 4b). These pioneering experiments allowed the iden-tification of hole transport through thiol-terminated molecular junctions, while also introducing a method to quantify S from statistically significant datasets. Following this work, our group measured the thermoelectric current through a molecular junction held under zero external bias voltage to determine S and the con-ductance through the same junction at a finite bias to determine G (ref. 92). Our measurements showed that amine-terminated mol-ecules conduct through the HOMO whereas pyridine-terminatedmolecules conduct through the LUMO (Fig. 4b) in good agree-ment with calculations.S has now been measured on a variety of molecular junctionsdemonstrating both hole and electron transport 91–95. Although the magnitude of S measured for molecular junctions is small, the fact that it can be tuned by changing the molecule makes these experiments interesting from a scientific perspective. Future work on the measurements of the thermal conductance at the molecu-lar level can be expected to establish a relation between chemical structure and the figure of merit, which defines the thermoelec-tric efficiencies of such devices and determines their viability for practical applications.SpintronicsWhereas most of the explorations of metal–molecule–metal junc-tions have been motivated by the quest for the ultimate minia-turization of electronic components, the quantum-mechanical aspects that are inherent to single-molecule junctions are inspir-ing entirely new device concepts with no classical analogues. In this section, we review recent experiments that demonstrate the capability of controlling spin (both electronic and nuclear) in single-molecule devices 96. The early experiments by the groups of McEuen and Ralph 97, and Park 98 in 2002 explored spin-depend-ent transport and the Kondo effect in single-molecule devices, and this topic has recently been reviewed in detail by Scott and Natelson 99. Here, we focus on new types of experiment that are attempting to control the spin state of a molecule or of the elec-trons flowing through the molecular junction. These studies aremotivated by the appeal of miniaturization and coherent trans-port afforded by molecular electronics, combined with the great potential of spintronics to create devices for data storage and quan-tum computation 100. The experimental platforms for conducting DOI: 10.1038/NNANO.2013.91。

高压断路器SF6压力低闭锁回路的优化

电力系统124丨电力系统装备 2018.5Electric System2018年第5期2018 No.5电力系统装备Electric Power System Equipment断路器的灭弧性能和绝缘性能在很大程度上取决于SF 6气体的密度,若断路器在密度不满足指标的情况下动作,将可能引起电弧未完全熄灭,继而烧毁绝缘,造成断路器爆炸等重大事故。

因此,对SF 6气体密度的监视显得尤为重要。

在检修过程中,经常会发现SF 6气压低闭锁功能失效,不能闭锁分合闸回路。