翻译资料1——SPI的访问

spi简介——精选推荐

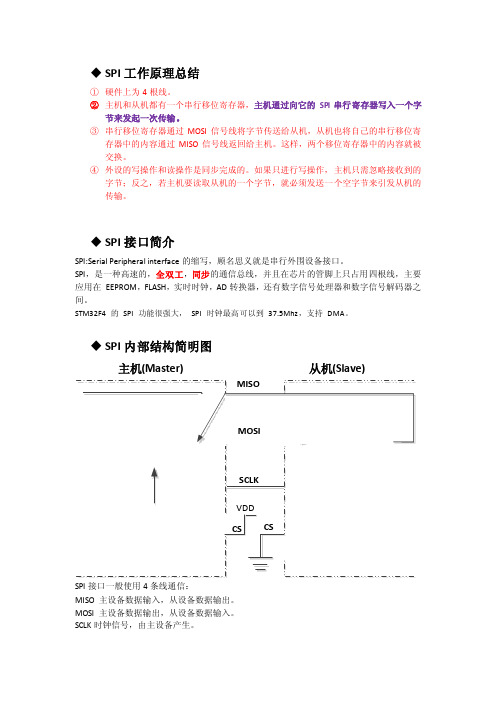

◆ SPI 工作原理总结① 硬件上为4根线。

② 主机和从机都有一个串行移位寄存器,主机通过向它的SPI 串行寄存器写入一个字节来发起一次传输。

③ 串行移位寄存器通过MOSI 信号线将字节传送给从机,从机也将自己的串行移位寄存器中的内容通过MISO 信号线返回给主机。

这样,两个移位寄存器中的内容就被交换。

④ 外设的写操作和读操作是同步完成的。

如果只进行写操作,主机只需忽略接收到的字节;反之,若主机要读取从机的一个字节,就必须发送一个空字节来引发从机的传输。

◆ SPI 接口简介SPI:Serial Peripheral interface 的缩写,顾名思义就是串行外围设备接口。

SPI ,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,主要应用在 EEPROM ,FLASH ,实时时钟,AD 转换器,还有数字信号处理器和数字信号解码器之间。

STM32F4 的 SPI 功能很强大, SPI 时钟最高可以到 37.5Mhz ,支持 DMA 。

◆ SPI 内部结构简明图移位寄存器移位寄存器SPI 时钟发生器MISO MOSI SCLKVDDCS CS主机(Master)从机(Slave)SPI 接口一般使用4条线通信:MISO 主设备数据输入,从设备数据输出。

MOSI 主设备数据输出,从设备数据输入。

SCLK 时钟信号,由主设备产生。

CS从设备片选信号,由主设备控制。

◆SPI接口框图⏹STM32 SPI接口可配置为支持SPI协议或者支持I2S音频协议,默认是SPI模式。

可以通过软件切换到I2S方式。

27.2.1 SPI 特性● 基于三条线的全双工同步传输● 基于双线的单工同步传输,其中一条可作为双向数据线● 8 位或16 位传输帧格式选择● 主模式或从模式操作● 多主模式功能● 8 个主模式波特率预分频器(最大值为f PCLK/2)● 从模式频率(最大值为f PCLK/2)● 对于主模式和从模式都可实现更快的通信● 对于主模式和从模式都可通过硬件或软件进行NSS 管理:动态切换主/从操作● 可编程的时钟极性和相位● 可编程的数据顺序,最先移位MSB或LSB● 可触发中断的专用发送和接收标志● SPI 总线忙状态标志● SPI TI 模式● 用于确保可靠通信的硬件CRC 功能:—在发送模式下可将CRC 值作为最后一个字节发送—根据收到的最后一个字节自动进行CRC 错误校验● 可触发中断的主模式故障、上溢和CRC 错误标志● 具有DMA 功能的1字节发送和接收缓冲器:发送和接收请求时钟相位和时钟极性通过SPI_CR1 寄存器中的CPOL 和CPHA 位,可以用软件选择四种可能的时序关系。

STM32固件库使用手册的中文翻译

创作编号:GB8878185555334563BT9125XW创作者:凤呜大王*UM0427用户手册32位基于ARM微控制器STM32F101xx与STM32F103xx固件函数库介绍本手册介绍了32位基于ARM微控制器STM32F101xx与STM32F103xx的固件函数库。

该函数库是一个固件函数包,它由程序、数据结构和宏组成,包括了微控制器所有外设的性能特征。

该函数库还包括每一个外设的驱动描述和应用实例。

通过使用本固件函数库,无需深入掌握细节,用户也可以轻松应用每一个外设。

因此,使用本固态函数库可以大大减少用户的程序编写时间,进而降低开发成本。

每个外设驱动都由一组函数组成,这组函数覆盖了该外设所有功能。

每个器件的开发都由一个通用API (application programming interface 应用编程界面)驱动,API对该驱动程序的结构,函数和参数名称都进行了标准化。

所有的驱动源代码都符合“Strict ANSI-C”标准(项目于范例文件符合扩充ANSI-C标准)。

我们已经把驱动源代码文档化,他们同时兼容MISRA-C 2004标准(根据需要,我们可以提供兼容矩阵)。

由于整个固态函数库按照“Strict ANSI-C”标准编写,它不受不同开发环境的影响。

仅对话启动文件取决于开发环境。

该固态函数库通过校验所有库函数的输入值来实现实时错误检测。

该动态校验提高了软件的鲁棒性。

实时检测适合于用户应用程序的开发和调试。

但这会增加了成本,可以在最终应用程序代码中移去,以优化代码大小和执行速度。

想要了解更多细节,请参阅Section 2.5。

因为该固件库是通用的,并且包括了所有外设的功能,所以应用程序代码的大小和执行速度可能不是最优的。

对大多数应用程序来说,用户可以直接使用之,对于那些在代码大小和执行速度方面有严格要求的应用程序,该固件库驱动程序可以作为如何设置外设的一份参考资料,根据实际需求对其进行调整。

SPI、I2C、UART三种串行总线的原理、区别及应用

简朴描述:SPI 和I2C这两种通信方式都是短距离旳,芯片和芯片之间或者其他元器件如传感器和芯片之间旳通信。

SPI和IIC是板上通信,IIC有时也会做板间通信,但是距离甚短,但是超过一米,例如某些触摸屏,手机液晶屏那些很薄膜排线诸多用IIC,I2C能用于替代原则旳并行总线,能连接旳多种集成电路和功能模块。

I2C是多主控总线,因此任何一种设备都能像主控器同样工作,并控制总线。

总线上每一种设备均有一种独一无二旳地址,根据设备它们自己旳能力,它们可以作为发射器或接受器工作。

多路微控制器能在同一种I2C总线上共存这两种线属于低速传播;ﻫ而UART是应用于两个设备之间旳通信,如用单片机做好旳设备和计算机旳通信。

这样旳通信可以做长距离旳。

UART和,UART就是我们指旳串口,速度比上面三者快,最高达100K左右,用与计算机与设备或者计算机和计算之间通信,但有效范畴不会很长,约10米左右,UART长处是支持面广,程序设计构造很简朴,随着USB旳发展,UART也逐渐走向下坡;SmBus有点类似于USB设备跟计算机那样旳短距离通信。

ﻫ简朴旳狭义旳说SPI和I2C是做在电路板上旳。

而UART和SMBUS是在机器外面连接两个机器旳。

具体描述:1、UART(TX,RX)就是两线,一根发送一根接受,可以全双工通信,线数也比较少。

数据是异步传播旳,对双方旳时序规定比较严格,通信速度也不是不久。

在多机通信上面用旳最多。

2、SPI(CLK,I/O,O,CS)接口和上面UART相比,多了一条同步时钟线,上面UART旳缺陷也就是它旳长处了,对通信双方旳时序规定不严格不同设备之间可以很容易结合,并且通信速度非常快。

一般用在产品内部元件之间旳高速数据通信上面,如大容量存储器等。

3、I2C(SCL,SDA)接口也是两线接口,它是两根线之间通过复杂旳逻辑关系传播数据旳,通信速度不高,程序写起来也比较复杂。

一般单片机系统里重要用来和24C02等小容易存储器连接。

SPI总线协议介绍

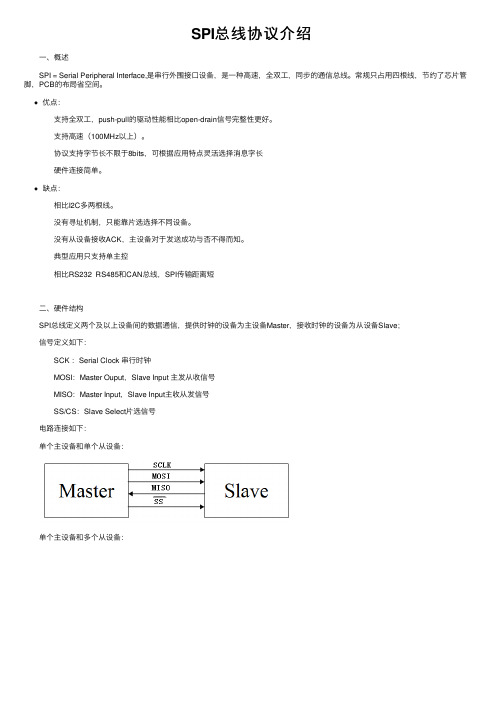

SPI总线协议介绍 ⼀、概述 SPI = Serial Peripheral Interface,是串⾏外围接⼝设备,是⼀种⾼速,全双⼯,同步的通信总线。

常规只占⽤四根线,节约了芯⽚管脚,PCB的布局省空间。

优点: ⽀持全双⼯,push-pull的驱动性能相⽐open-drain信号完整性更好。

⽀持⾼速(100MHz以上)。

协议⽀持字节长不限于8bits,可根据应⽤特点灵活选择消息字长 硬件连接简单。

缺点: 相⽐I2C多两根线。

没有寻址机制,只能靠⽚选选择不同设备。

没有从设备接收ACK,主设备对于发送成功与否不得⽽知。

典型应⽤只⽀持单主控 相⽐RS232 RS485和CAN总线,SPI传输距离短 ⼆、硬件结构 SPI总线定义两个及以上设备间的数据通信,提供时钟的设备为主设备Master,接收时钟的设备为从设备Slave; 信号定义如下: SCK :Serial Clock 串⾏时钟 MOSI:Master Ouput,Slave Input 主发从收信号 MISO:Master Input,Slave Input主收从发信号 SS/CS:Slave Select⽚选信号 电路连接如下: 单个主设备和单个从设备: 单个主设备和多个从设备: 三、寄存器类型 摩托罗拉定义的SPI寄存器包括: SPI Control Register 1 控制寄存器1 SPI Control Register 2 控制寄存器2 SPI Baud Rate Register 波特率寄存器 SPI Status Register(SPISR) 状态寄存器(只读其余均可读可写) SPI Data Register(SPIDR)数据寄存器 通过往寄存器中写⼊不同的值,设置SPI模块的不同属性 四、SPI传输模式 SPI通信有四种模式,简单地讲就是设置SCLK时钟信号线的那种信号为有效信号 通过设置控制寄存器SPICR1中的CPOL和CPHA位,将SPI可以分成四种传输模式 时钟极性CPOL,即Clock Polarity,决定时钟空闲时状态电平。

SPI、I2C、UART三种串行总线协议的区别和SPI接口介绍(转)

SPI、I2C、UART三种串⾏总线协议的区别和SPI接⼝介绍(转)SPI、I2C、UART三种串⾏总线协议的区别第⼀个区别当然是名字:SPI(Serial Peripheral Interface:串⾏外设接⼝);I2C(INTER IC BUS)UART(Universal Asynchronous Receiver Transmitter:通⽤异步收发器)第⼆,区别在电⽓信号线上:SPI总线由三条信号线组成:串⾏时钟(SCLK)、串⾏数据输出(SDO)、串⾏数据输⼊(SDI)。

SPI总线可以实现多个SPI设备互相连接。

提供SPI串⾏时钟的SPI设备为SPI主机或主设备(Master),其他设备为SPI从机或从设备(Slave)。

主从设备间可以实现全双⼯通信,当有多个从设备时,还可以增加⼀条从设备选择线。

如果⽤通⽤IO⼝模拟SPI总线,必须要有⼀个输出⼝(SDO),⼀个输⼊⼝(SDI),另⼀个⼝则视实现的设备类型⽽定,如果要实现主从设备,则需输⼊输出⼝,若只实现主设备,则需输出⼝即可,若只实现从设备,则只需输⼊⼝即可。

I2C总线是双向、两线(SCL、SDA)、串⾏、多主控(multi-master)接⼝标准,具有总线仲裁机制,⾮常适合在器件之间进⾏近距离、⾮经常性的数据通信。

在它的协议体系中,传输数据时都会带上⽬的设备的设备地址,因此可以实现设备组⽹。

如果⽤通⽤IO⼝模拟I2C总线,并实现双向传输,则需⼀个输⼊输出⼝(SDA),另外还需⼀个输出⼝(SCL)。

(注:I2C资料了解得⽐较少,这⾥的描述可能很不完备)UART总线是异步串⼝,因此⼀般⽐前两种同步串⼝的结构要复杂很多,⼀般由波特率产⽣器(产⽣的波特率等于传输波特率的16倍)、UART接收器、UART发送器组成,硬件上由两根线,⼀根⽤于发送,⼀根⽤于接收。

显然,如果⽤通⽤IO⼝模拟UART总线,则需⼀个输⼊⼝,⼀个输出⼝。

第三,从第⼆点明显可以看出,SPI和UART可以实现全双⼯,但I2C不⾏;第四,看看⽜⼈们的意见吧!wudanyu:I2C线更少,我觉得⽐UART、SPI更为强⼤,但是技术上也更加⿇烦些,因为I2C需要有双向IO的⽀持,⽽且使⽤上拉电阻,我觉得抗⼲扰能⼒较弱,⼀般⽤于同⼀板卡上芯⽚之间的通信,较少⽤于远距离通信。

SPI 4.0翻译DOC

SPI协议翻译专有名词第一章、简介图1-1概述了SPI的基本架构。

SPI的主要组成部分是状态、控制盒数据寄存器,移位逻辑,波特率发生器,主从控制逻辑和端口控制逻辑。

图1-1 SPI框图1.1概述SPI模块允许在MCU和外设之间进行双工,同步,串行通信。

软件可投票决定SPI的状态标志或者说SPI的操作可以被中断。

1.2特性SPI包含这些独特的特性:(1)主模式和从模式(2)双向模式(3)从选择输出(4)CPU的模式错误标志中断能力(5)双缓冲数据寄存器(6)串行时钟的极性和相位可编程(7)对SPI在等待模式期间的操作控制1.3各种模式的操作SPI有三种工作模式,运行,等待和停止模式。

(1)运行模式这个是基本运行模式(2)等待模式SPI运行在等待模式的时候是一个可配置的低功耗的模式,被SPICR2中的SPISWAI位控制。

在等待模式下,如果SPIWAI位是清0的,SPI就像运行在运行模式下一样。

如果SPIWAI位是置位的,SPI就会进入功率保持状态,SPI的时钟产生被关闭。

如果SPI被配置成一个主机,任何传输都被停止,但是当CPU进入运行模式的时候将重新开始。

如果SPI被配置成一个从机,接收和传输一个byte继续,所以从机一直与主机保持同步。

(3)停止模式SPI在这个模式下为了减少功耗是保守的(低功耗)。

如果SPI被配置成一个主机,任何传输都会被停止,当CPU进入运行模式后会继续。

如果SPI 被配置成一个从机,接收和传输一个byte继续,所以从机一直保持与主机同步。

这些只是高层面上的说明,详细的模式操作说明被包含在4.8低功耗模式设置。

第二章、外部信号说明2.1概述本节列出的名称和端口包括所有输入和输出,或者各种可能性,芯片之间的连接。

SPI模块有4个外引脚。

2.2 详细的信号的描述2.2.1 MOSI当SPI被配置成主机时这个引脚被用于传输数据,被配置成从机的时候这个引脚被用于接收数据。

2.2.2 MISO当SPI被配置成从机时这个引脚被用于传输数据,被配置成主机的时候这个引脚被用于接收数据。

SPI的接口及其应用

SPI的接口及其应用2010-09-01 00:10:29| 分类:ARM及程序设计| 标签:|字号大中小订阅1 SPI接口的特点目前很多单片机都配置有SPI、I2C或UART等串行接口。

在SPI、I2C及UART三种串行接口一般情况下速度最快的是SPI。

I2C接口由于是二线协议速度很难超过1MHz/ Bit,而UART工作在方式0(8位移位寄存器)时时钟速度为系统时钟的十二分之一(Fosc/12),而SPI接口时钟速度一般为系统时钟的四分之一(Fosc/4)。

典型SPI接口结构如图1所示。

串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola公司推出的一种同步串行接口,Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。

SPI 用于CPU与各种外围器件进行全双工、同步串行通讯。

SPI可以同时发出和接收串行数据。

它只需四条线就可以完成MCU与各种外围器件的通讯,这四条线是:串行时钟线(CSK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效从机选择线CS。

这些外围器件可以是简单的TTL移位寄存器,复杂的LCD显示驱动器,A/D、D/A转换子系统或其他的MCU。

当SPI工作时,在移位寄存器中的数据逐位从输出引脚(MOSI)输出(高位在前),同时从输入引脚(MISO)接收的数据逐位移到移位寄存器(高位在前)。

发送一个字节后,从另一个外围器件接收的字节数据进入移位寄存器中。

主SPI的时钟信号(SCK)使传输同步。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

图2和图3中还给出了SPI总线工作的四种方式及SPI总线接口的时序。

SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

SPI和IIC详解

工通信的特性。SPI总线上所有的传输都参照一个共同的时钟,这个同 步时钟信号由主设备产生。接收数据的从设备使用时钟对串行比特流 的接收进行同步化。

2

SPI总线协议

四条信号线: MISO(主机输入/从机输出) MOSI(主机输出/从机输入) SCLK(串行时钟) CS或SS (外设片选或从机选择) 特点: 全双工(输入/输出独立) 同步(带有时钟线) 物理结构简单 灵活性强

SCL; 2、每个连接到总线的器件都可以通过唯一的地址和一直存在的简 单的主机/从机关系软件设定地址,主机可以作为主机发送器或主 机接收器; 3、它是一个真正的多主机总线,如果两个或更多主机同时初始化 ,数据传输可以通过冲突检测和仲裁防止数据被破坏; 4、串行的8 位双向数据传输位速率在标准模式下可达100kbit/s,快 速模式下可达400kbit/s,高速模式下可达3.4Mbit/s; 5、连接到相同总线的IC 数量只受到总线的最大电容400pF 限制。

LSBFIRST:

发送帧格式 SPE: SPI使能 BR[2:0]: 波特率控制 MSTR: 主/从设置 CPOL/CPHA: 时钟极性/相位

13

控制寄存器SPI_CR2

中断使能设置: TXEIE: 发送缓冲区空中断使能 RXNEIE: 接收缓冲区非空中断使能 ERRIE: 错误中断使能

I2C通过串行数据(SDA)线和串行时钟 (SCL)线在连接到总线的器

件间传递信息。每个器件都有一个唯一的地址识别(无论是微控制器 ——MCU、LCD 驱动器、存储器或键盘接口),而且都可以作为一个 发送器或接收器(由器件的功能决定)。

第二节通讯及总线-SPI总线

验位),根据事先的配置或约定

精品PPT

SPI总线(zǒnɡ xiàn)协议

• SPI,是英语(yīnɡ yǔ)Serial Peripheral interface的缩写,顾

名思义就是串行外围设备接口。是Motorola首先在其

MC68HCXX 系列处理器上定义的。

temp |= 0x0008;//定义波特率为18M Hz

temp |= 0x0003;//定义极性及相位关系,为11

temp &=0xF77F;//定义8位数据格式,且高位在前传输

temp |= 0x0200;//NSS引脚工作在软件模式下

temp |= 0x0042;//配置(pèizhì)为主模式,并启动SPI

• 有2种NSS模式:

• 软件NSS模式:设置SPI_CR1寄存器的SSM位来使能这种模式。

在这种模式下NSS引脚可以用作它用,而内部NSS信号电平可以通

过写SPI_CR1的SSI位来驱动

精品PPT

• 从选择(NSS)脚管理

• 硬件NSS模式(móshì),分两种情况:

• NSS输出被使能:当STM32为主SPI,并且NSS输出已经

GPIO_Init(GPIOA, &GPIO_InitStructure);

精品PPT

Stm32之SPI配置(pèizhì)

•

Step 3:spi参数配置

•

根据(gēnjù)SPI原理,可将器件配置为主设备和从设备。

•

以基于SPI的flash访问为例,将STM32配置为主设备,外部存储器

flash型号为:M25P64

精品PPT

SD卡的SPI模式(中文)

7.2.3 读数据 SPI支持单块读和多块读操作(在SD存储卡协议中的CMD17 OR CMD18)。当接收一个有效的读命令后卡将在一个在SET_BLOCK_LEN(CMD16)定义 了长度的数据令牌之后,用一个响应令牌作出回复。(参考Figure41)

Figure41 单块读操作

一个有效的数据块被添加了一个16位CRC,此CRC由CCITT标准多项式X16+X12+X5+1生成。 能被READ_BL_LEN给出的最大的块的的长度大CSD中定义了。如果片块被允许,块长度可以是1~MAX块大小之间的任何长度。否则,数据读的有 效块长度只是在READ_BL_LEN中给出的值。 起始地址可以是在卡的有效地址范围内的任何字节地址。但是,每一个块,必须包含入一个单一的物理卡扇区中。 如发生一个可修复错误,卡不会传输任何数据,而是发送一个特定的数据错误令牌到主机。

7.2.7 复位序列 SD卡需要一个定义了的复位序列。上电复位或CMD0之后,卡进入了空闲模式。在这个模式中,合法的主机命令只有CMD1、ACMD41、CMD58。 在SPI模式下,CMD1和ACMD41都有同样的行为。

/bbs/view_4_3477.html(第 3/8 页)2010-9-4 下午 22:05:51

请参考英文原版。

7.2.10 卡片 锁定/解锁

请参考英文原版。

7.2版。

7.2.12 版权保护命令

请参考英文原版。

7.3 SPI模式事务包

7.3.1 命令令牌 1、命令格式 所有的SD存储卡命令都是6字节长。命令的传输总是以相应的命令代码字的左边位开始。所有的命令由CRC保护。命令的参数由以下表给出。 2、命令集 如SD模式一样,SPI命令分成几个集合。每一个集合支持一类的功能。在这两种通信模式下,SD存储卡都支持同组的可选命令集。 3、命令详细说明 下表给出了一个SPI模式总线命令集的详细说明.响应在7。3。2中定义了。表57列出了所有SD存储卡命令。SPI 模式的“YES”表示此命令在SPI模式下 被支持。由于这此限制,CSD中此命令集描述仍有效。如果一个命令不需要参数argument,此域的值应该设为零。被保留的命令在SD 模式中也是被 保留。命令的二进制代码通过记忆标志来定义。举一个例子,command index域的内容是二进制的“000000”(CMD0)和“100111”(CMD39)。 Table57:命令和argument

SPI的项目接口说明

极性1

SCK (CPOL = 1)

从机选择

SSEL

时钟相位 为0

时钟前沿 数据采样 时钟后沿 数据输出

CPHA = 0 Cycle # CPHA = 0 MOSI (CPHA = 0) MISO (CPHA = 0)

时钟相位为 1

时钟前沿数 据输出 时钟后沿数 据采样

CPHA = 1 Cycle # CPHA = 1 MOSI (CPHA = 1) MISO (CPHA = 1)

SPI寄存器描述——SPI模式寄存器

PCS: 外设片选;该域仅适用于固定外设选择有效(PS = 0)。

若PCSDEC = 0:PCS = xxx0

NPCS[3:0] = 1110;

PCS = xx01

NPCS[3:0] = 1101;

PCS = x011

NPCS[3:0] = 1011;

PCS = 0111

根据学习、总结,形成一个较完备的多路中间件SPI总线设备的驱动框架结 构:实现要求:A方便后续SPI设备扩展;B方便实时、高速、大容量数据 流的读写;C存在数据信息的容错处理机制,避免数据错误的产生等。

多线程处理机制,处理方法如何实现,(本处所指spi驱动,并不一定是 FLASH存储器件,如可以是A/D、液晶、无线处理单元、gps模块等)如液 晶显示初始化、同时大批量开关量数据流需要向FLASH中存储数据时,处 理机制是怎样的………………

SPI寄存器描述——SPI状态寄存器

OVRES: 溢出错误状态 0 = 上次读SPI_SR 后未检测到溢出错误。 1 = 上次读SPI_SR 后出现溢出错误。 上次读SPI_RDR 后当SPI_RDR 至少两次载入串行器,出溢出错误。

ENDRX: RX 缓冲结束 0 = 上次写SPI_RCR 或SPI_RNCR 后接收计数寄存器仍未达到0。 1 = 上次写SPI_RCR 或SPI_RNCR 后接收计数寄存器已达到0。

SPI接口详细讲解

• CPOL(时钟极性)=0; • 上升沿发送、下降沿接收、高位先发送。 • 上升沿到来的时候,MOSI上的电平将被发送到从设备

的寄存器中。 • 下降沿到来的时候,MISO上的电平将被接收到主设备

的寄存器中。 • 假设主机和从机初始化就绪:并且主机的sbuf=0xaa

(10101010),从机的sbuf=0x55 (01010101),下面将分步 对SPI的8个时钟周期的数据情况演示一遍(假设上升沿发 送数据)。Sbuf(串行接收和发射缓冲器)

7

脉冲

0 1↑ 1↓ 2↑ 2↓ 3↑ 3↓ 4↑ 4↓ 5↑ 5↓ 6↑ 6↓ 7↑ 7↓ 8↑

1

2021/6/4

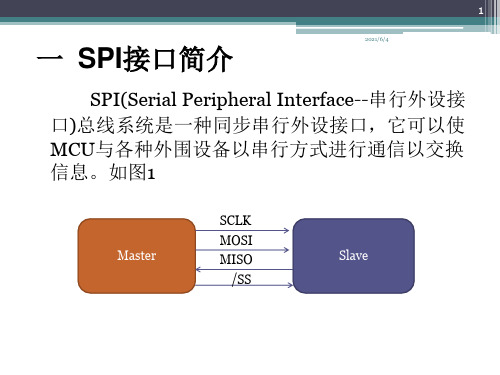

一 SPI接口简介

SPI(Serial Peripheral Interface--串行外设接 口)总线系统是一种同步串行外设接口,它可以使 MCU与各种外围设备以串行方式进行通信以交换 信息。如图1

Master

SCLK MOSI Mபைடு நூலகம்SO

/SS

Slave

2

2021/6/4

• (1)MOSI – 主设备数据输出,从设备数据输入 • (2)MISO – 主设备数据输入,从设备数据输出 • (3)SCLK – 时钟信号,由主设备产生 • (4)/SS – 从设备使能信号,由主设备控制

主机sbuff 10101010 0101010X 01010100 1010100X 10101001 0101001X 01010010 1010010X 10100101 0100101X 01001010 1001010X 10010101 0010101X 00101010 0101010X

SPI通信的总结

STM32---SPI通信的总结(库函数操作)本文主要由7项内容介绍SPI并会在最后附上测试源码供参考:1.SPI的通信协议2.SPI通信初始化(以STM32为从机,LPC1114为主机介绍)3.SPI的读写函数4.SPI的中断配置5.SPI的SMA操作6.测试源码7.易出现的问题及原因和解决方法一、SPI的通信协议SPI(Serial Peripheral Interface)是一种串行同步通讯协议,由一个主设备和一个或多个从设备组成,主设备启动一个与从设备的同步通讯,从而完成数据的交换。

SPI 接口一般由4根线组成,CS片选信号(有的单片机上也称为NSS),SCLK时钟信号线,MISO数据线(主机输入从机输出),MOSI数据线(主机输出从机输入),CS 决定了唯一的与主设备通信的从设备,如没有CS 信号,则只能存在一个从设备,主设备通过产生移位时钟信号来发起通讯。

通讯时主机的数据由MISO输入,由MOSI 输出,输入的数据在时钟的上升或下降沿被采样,输出数据在紧接着的下降或上升沿被发出(具体由SPI的时钟相位和极性的设置而决定)。

二、以STM32为例介绍SPI通信1.STM32f103 带有3个SPI模块其特性如下:2SPI 初始化初始化SPI 主要是对SPI要使用到的引脚以及SPI通信协议中时钟相位和极性进行设置,其实STM32的工程师已经帮我们做好了这写工作,调用库函数,根据自己的需要来修改其中的参量来完成自己的配置即可,主要的配置是如下几项:●引脚的配置SPI1的SCLK, MISO ,MOSI分别是PA5,PA6,PA7引脚,这几个引脚的模式都配置成GPIO_Mode_AF_PP 复用推挽输出(关于GPIO 的8种工作模式如不清楚请自己百度,在此不解释),如果是单主单从,CS引脚可以不配置,都设置成软件模式即可。

●通信参数的设置1.SPI_Direction_2Lines_FullDuplex把SPI设置成全双工通信;2.在SPI_Mode 里设置你的模式(主机或者从机),3.SPI_DataSize是来设置数据传输的帧格式的SPI_DataSize_8b是指8位数据帧格式,也可以设置为SPI_DataSize_16b,即16位帧格式4.SPI_CPOL和SPI_CPHA是两个很重要的参数,是设置SPI通信时钟的极性和相位的,一共有四种模式在库函数中CPOL有两个值SPI_CPOL_High(=1)和SPI_CPOL_Low ( =0). CPHA有两个值SPI_CPHA_1Edge (=0) 和SPI_CPHA_2Edge(=1)CPOL表示时钟在空闲状态的极性是高电平还是低电平,而CPHA则表示数据是在什么时刻被采样的,手册中如下:我的程序中主、从机的这两位设置的相同都是设置成1,即空闲时时钟是高电平,数据再第二个时钟沿被采样,实验显示数据收发都正常。

SPI总线通俗易懂讲解

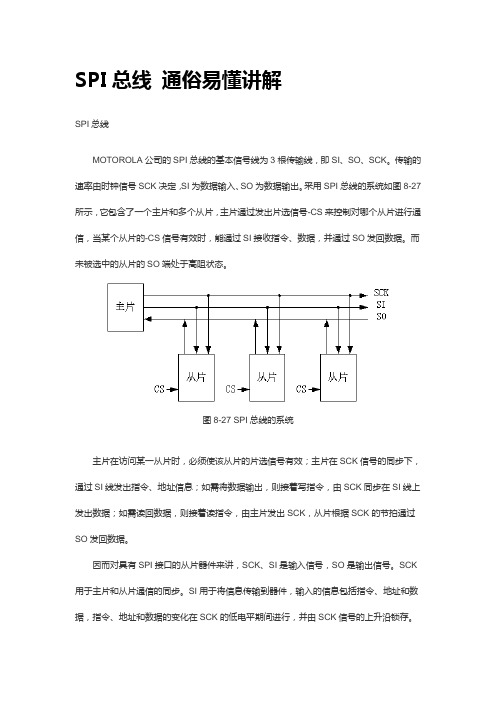

SPI总线通俗易懂讲解SPI总线MOTOROLA公司的SPI总线的基本信号线为3根传输线,即SI、SO、SCK。

传输的速率由时钟信号SCK决定,SI为数据输入、SO为数据输出。

采用SPI总线的系统如图8-27所示,它包含了一个主片和多个从片,主片通过发出片选信号-CS来控制对哪个从片进行通信,当某个从片的-CS信号有效时,能通过SI接收指令、数据,并通过SO发回数据。

而未被选中的从片的SO端处于高阻状态。

图8-27 SPI总线的系统主片在访问某一从片时,必须使该从片的片选信号有效;主片在SCK信号的同步下,通过SI线发出指令、地址信息;如需将数据输出,则接着写指令,由SCK同步在SI线上发出数据;如需读回数据,则接着读指令,由主片发出SCK,从片根据SCK的节拍通过SO发回数据。

因而对具有SPI接口的从片器件来讲,SCK、SI是输入信号,SO是输出信号。

SCK 用于主片和从片通信的同步。

SI用于将信息传输到器件,输入的信息包括指令、地址和数据,指令、地址和数据的变化在SCK的低电平期间进行,并由SCK信号的上升沿锁存。

SO用于将信息从器件传出,传出的信息包括状态和数据,信息在SCK信号的下降沿移出。

Microchip公司的25XX系列的串行E2PROM采用了SPI总线,该系列器件的性能如表8-2所示。

表8-2 Microchip公司的25XX系列的串行E2PROM型号25XX04025XX08025XX16025XX320容量4K(512 X 8bit)8K(1024 X 8bit)16K(4096 X 8bit)32K(4096 X 8bit)地址信号A0~A8A0~A9A0~A10A0~A11以25XX320为例,该器件是4K字节的E2PROM,结构如图8-28所示,接口信号为SCK、SI和SO,此外还具有-CS、-WP、-HOLD信号线。

其中-CS为器件选中信号,当此信号为低电平时器件被选中,高电平时器件处于等待状态。

spi

SPI总线简介SPI总线基本概念SPI ( Serial Peripheral Interface ———串行外设接口) 总线是Motorola公司推出的一种同步串行接口技术。

SPI总线系统是一种同步串行外设接口,允许MCU 与各种外围设备以串行方式进行通信、数据交换。

外围设备包括FLASHRAM、A/ D 转换器、网络控制器、MCU 等。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

其工作模式有两种:主模式和从模式。

SPI是一种允许一个主设备启动一个从设备的同步通讯的协议,从而完成数据的交换。

也就是SPI是一种规定好的通讯方式。

这种通信方式的优点是占用端口较少,一般4根就够基本通讯了(不算电源线)。

同时传输速度也很高。

一般来说要求主设备要有SPI控制器(也可用模拟方式),就可以与基于SPI的芯片通讯了。

SPI总线系统结构SPI 系统可直接与各个厂家生产的多种标准外围器件直接接口,一般使用4 条线:串行时钟线(SCK) 、主机输入/ 从机输出数据线MISO(DO)、主机输出/ 从机输入数据线MOSI (DI)和低电平有效的从机选择线CS。

MISO和MOSI用于串行接收和发送数据,先为MSB(高位),后为LSB(低位)。

在SPI设置为主机方式时,MISO是主机数据输入给,MOSI 是主机数据输出线。

SCK用于提供时钟脉冲将数据一位位地传送。

SPI总线器件间传送数据框图如图3所示:图3 SPI总线器件间传送数据框图SPI总线的接口特性利用SPI总线可在软件的控制下构成各种系统。

如1个主MCU和几个从MCU、几个从MCU相互连接构成多主机系统(分布式系统)、1个主MCU和1个或几个从I/O设备所构成的各种系统等。

在大多数应用场合,可使用1个MCU作为主控机来控制数据,并向1个或几个从外围器件传送该数据。

SPI 接口协议介绍

SCLK N2 輸出

SCLK 輸入

DATA N2 輸出

DATA 輸入

2021/1/29

16

其它序列接口簡介

2.MicroWire 接口

➢ A. MicroWire接口介紹 MicroWire是由National Semiconductor開發出來的全

雙工同步主/從設備通信協議 ,它是個三條線的協定。

3↑ 0101001X 1010110X 0 1 7↑ 0010101X 1101010X 0 1

3↓ 01010010 10101101 0 1 7↓ 00101010 11010101 0 1

4↑ 1010010X 0101101X 1 0 8↑ 0101010X 1010101X 1 0

4↓ 10100101 01011011 1 0 8↓ 01010101 10101010 1 0

➢ C.1-Wire時序圖:

2021/1/29

19

其它序列接口簡介

4. RS-232接口

➢ A.RS-232 接口介紹 幾乎所有的電腦都採用TIA/EIA-232-F(通常稱為RS-232)

介面方式。RS-232是一種點對點接口,適用於中等長度的 通訊,速率可高達20Kbps。

RS-232可在兩對接收/發送器(稱為數據終端設備(DTE)及 數據電路終端設備(DCE))間進行全雙工通訊。每一端的傳輸 信號均與另一端的接收信號相連。因此,兩端的引腳有所不 同。

2021/1/29

17

其它序列接口簡介

3. 1-Wire接口

➢ A. 1-Wire接口介紹 1-Wire是由Dallas Semiconductor開發出來的半雙工非

同步主/從式﹐但沒有用於多個主設備的通信協議。

总线SPI解释

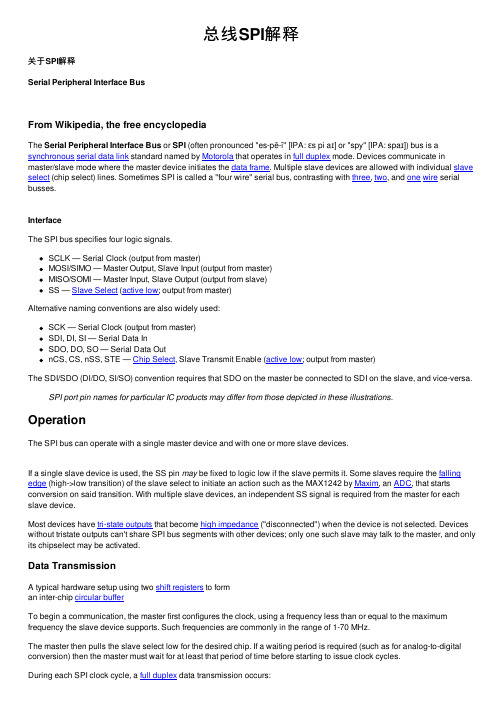

总线SPI解释关于SPI解释Serial Peripheral Interface BusFrom Wikipedia, the free encyclopediaThe Serial Peripheral Interface Bus or SPI (often pronounced "es-pē-ī" [IPA: ɛs pi aɪ] or "spy" [IPA: spaɪ]) bus is a synchronous serial data link standard named by Motorola that operates in full duplex mode. Devices communicate in master/slave mode where the master device initiates the data frame. Multiple slave devices are allowed with individual slave select (chip select) lines. Sometimes SPI is called a "four wire" serial bus, contrasting with three, two, and one wire serial busses.InterfaceThe SPI bus specifies four logic signals.SCLK — Serial Clock (output from master)MOSI/SIMO — Master Output, Slave Input (output from master)MISO/SOMI — Master Input, Slave Output (output from slave)SS — Slave Select (active low; output from master)Alternative naming conventions are also widely used:SCK — Serial Clock (output from master)SDI, DI, SI — Serial Data InSDO, DO, SO — Serial Data OutnCS, CS, nSS, STE — Chip Select, Slave Transmit Enable (active low; output from master)The SDI/SDO (DI/DO, SI/SO) convention requires that SDO on the master be connected to SDI on the slave, and vice-versa.SPI port pin names for particular IC products may differ from those depicted in these illustrations.OperationThe SPI bus can operate with a single master device and with one or more slave devices.If a single slave device is used, the SS pin may be fixed to logic low if the slave permits it. Some slaves require the falling edge (high->low transition) of the slave select to initiate an action such as the MAX1242 by Maxim, an ADC, that starts conversion on said transition. With multiple slave devices, an independent SS signal is required from the master for each slave device.Most devices have tri-state outputs that become high impedance ("disconnected") when the device is not selected. Devices without tristate outputs can't share SPI bus segments with other devices; only one such slave may talk to the master, and only its chipselect may be activated.Data TransmissionA typical hardware setup using two shift registers to forman inter-chip circular bufferTo begin a communication, the master first configures the clock, using a frequency less than or equal to the maximum frequency the slave device supports. Such frequencies are commonly in the range of 1-70 MHz.The master then pulls the slave select low for the desired chip. If a waiting period is required (such as for analog-to-digital conversion) then the master must wait for at least that period of time before starting to issue clock cycles.During each SPI clock cycle, a full duplex data transmission occurs:the master sends a bit on the MOSI line; the slave reads it from that same linethe slave sends a bit on the MISO line; the master reads it from that same lineNot all transmissions require all four of these operations to be meaningful but they do happen.Transmissions normally involve two shift registers of some given word size, such as eight bits, one in the master and one in the slave; they are connected in a ring. Data is usually shifted out with the most significant bit first, while shifting a new least significant bit into the same register. After that register has been shifted out, the master and slave have exchanged register values. Then each device takes that value and does something with it, such as writing it to memory. If there is more data to exchange, the shift registers are loaded with new data and the process repeats.Transmissions may involve any number of clock cycles. When there are no more data to be transmitted, the master stops toggling its clock. Normally, it then deselects the slave.Transmissions often consist of 8-bit words, and a master can initiate multiple such transmissions if it wishes/needs. However, other word sizes are also common, such as 16-bit words for touchscreen controllers or audio codecs, like the TSC2101 from Texas Instruments; or 12-bit words for many digital-to-analog or analog-to-digital converters.Every slave on the bus that hasn't been activated using its slave select line must disregard the input clock and MOSI signals, and may not drive MISO. The master selects only one slave at a time.[edit] Clock polarity and phaseA timing diagram showing clock polarity and phaseIn addition to setting the clock frequency, the master must also configure the clock polarity and phase with respect to the data. Freescale's SPI Block Guide [1] names these two options as CPOL and CPHA respectively, and most vendors have adopted that convention.The timing diagram is shown to the right. The timing is further described below and applies to both the master and the slave device.At CPOL=0 the base value of the clock is zeroFor CPHA=0, data are read on the clock's rising edge (low->high transition) and data are changed on a fallingedge (high->low clock transition).For CPHA=1, data are read on the clock's falling edge and data are changed on a rising edge.At CPOL=1 the base value of the clock is one (inversion of CPOL=0)For CPHA=0, data are read on clock's falling edge and data are changed on a rising edge.For CPHA=1, data are read on clock's rising edge and data are changed on a falling edge.That is, CPHA=0 means sample on the leading (first) clock edge, while CPHA=1 means sample on the trailing (second) clock edge, regardless of whether that clock edge is rising or falling. Note that with CPHA=0, the data must be stable for a half cycle before the first clock cycle. Also, note that no matter what the CPOL and CPHA modes say, the initial clock value must be stable before the chip select line goes active.This adds more flexibility to the communication channel between the master and slave.[edit] Mode NumbersThe combinations of polarity and phases are often referred to as modes which are commonly numbered according to the following convention, with CPOL as the high order bit and CPHA as the low order bit:Mode CPOL CPHA000101210311[edit] Independent slave SPI configurationTypical SPI bus: master and three independentslavesIn the independent slave configuration, there is an independent slave select line for each slave. This is the way SPI isnormally used. Since the MISO pins of the slaves are connected together, they are required to be tri-state pins.Daisy chain SPI configurationDaisy-chained SPI bus: master and cooperativeslavesSome products with SPI bus are designed to be capable of being connected in a daisy chain configuration, the first slave output being connected to the second slave input, etc. The SPI port of each slave is designed to send out during the second group of clock pulses an exact copy of what it received during the first group of clock pulses. The whole chain acts as an SPI communication shift register; daisy chaining is often done with shift registers to provide a bank of inputs or outputs through SPI. Such a feature only requires a single SS line from the master, rather than a separate SS line for each slave.This somewhat resembles SGPIO, although SGPIO is limited to particular backplane management activities and would not interoperate with most SPI chips.Valid SPI communicationsSome slave devices are designed to ignore any SPI communications in which the number of clock pulses is greater than specified. Others don't care, ignoring extra inputs and continuing to shift the same output bit. It is common for different devices to use SPI communications with different lengths, as, for example, when SPI is used to access the scan chain of a digital IC by issuing a command word of one size (perhaps 32 bits) and then getting a response of a different size (perhaps 153 bits, one for each pin in that scan chain).InterruptsSPI devices sometimes use another signal line to send an interrupt signal to a host CPU. Examples include pen-down interrupts from touchscreen sensors, thermal limit alerts from temperature sensors, alarms issued by real time clock chips, and headset jack insertions from the sound codec in a cell phone.Pros and cons of SPIAdvantagesFull duplex communicationHigher throughput than I²C or SMBusComplete protocol flexibility for the bits transferredNot limited to 8-bit wordsArbitrary choice of message size, content, and purposeExtremely simple hardware interfacingTypically lower power requirements than I²C or SMBus due to less circuitry (including pullups)No arbitration or associated failure modesSlaves use the master's clock, and don't need precision oscillatorsTransceivers are not neededUses many fewer pins on IC packages, and wires in board layouts or connectors, than parallel interfacesAt most one "unique" bus signal per device (chipselect); all others are sharedDisadvantagesRequires more pins on IC packages than I²C, even in the "3-Wire" variantNo in-band addressing; out-of-band chip select signals are required on shared bussesNo hardware flow controlNo slave acknowledgment (the master could be "talking" to nothing and not know it)Can operate with only one master deviceWithout a formal standard, validating conformance is not possibleOnly handles short distances compared to RS-232, RS-485, or CAN-bus。

(最新整理)SPI协议及工作原理分析

SPI协议及工作原理分析编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(SPI协议及工作原理分析)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为SPI协议及工作原理分析的全部内容。

SPI协议及工作原理分析一、概述。

SPI, Serial Perripheral Interface, 串行外围设备接口, 是 Motorola 公司推出的一种同步串行接口技术. SPI 总线在物理上是通过接在外围设备微控制器(PICmicro) 上面的微处理控制单元(MCU)上叫作同步串行端口(Synchronous Serial Port)的模块(Module)来实现的, 它允许 MCU 以全双工的同步串行方式, 与各种外围设备进行高速数据通信.SPI 主要应用在 EEPROM, Flash, 实时时钟(RTC), 数模转换器(ADC), 数字信号处理器(DSP)以及数字信号解码器之间。

它在芯片中只占用四根管脚(Pin)用来控制以及数据传输,节约了芯片的 pin 数目,同时为 PCB 在布局上节省了空间. 正是出于这种简单易用的特性, 现在越来越多的芯片上都集成了 SPI技术.二、特点1. 采用主—从模式(Master-Slave)的控制方式SPI 规定了两个SPI 设备之间通信必须由主设备(Master) 来控制次设备(Slave)。

一个 Master 设备可以通过提供 Clock 以及对 Slave 设备进行片选(Slave Select) 来控制多个 Slave 设备, SPI 协议还规定 Slave 设备的 Clock 由 Master 设备通过 SCK 管脚提供给 Slave 设备, Slave 设备本身不能产生或控制 Clock,没有 Clock 则Slave 设备不能正常工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

串行外围接口SPI的访问

作者:Siri Namtvedt 关键字:

• CC1100 • CC1101 • CC1150 • CC2500 • CC2550 • SPI

•复位

•突发访问•命令滤波

1 简介

本设计说明的目的是让我们了解该如何配置SPI接口使其能够与CC1100/CC1101/CC1150/CC2500/CC2550连接,并且告诉我们要如何理解状态字节,以及复位开关在SPI接口上是怎么实现的,另外也描述了我们可以使用的不同SPI接口的访问(读/写,单址访问/突发访问以及命令滤波)。

目录

1简介 (1)

2缩写词 (3)

3SPI接口 (3)

3.1SPI接口配置 (3)

3.2 SPI接口的时间要求 (4)

3.3 SPI的访问 (4)

3.4单字节访问 (5)

3.5突发访问 (5)

3.6命令滤波 (5)

4芯片的状态字节 (7)

5复位 (9)

6总说明 (10)

2 缩写词

MCU 微控制器单元

SPI 串行外围接口

3 SPI接口

CC1100/CC1101/CC1150/CC2500/CC2550的接口配置为一个简单的4线SPI兼容接口(SI, SO, SCLK和CSn),在这里无线电受到MCU的控制。

这个接口也可以同时用作写或读缓存数据。

在SPI接口上传输的所有地址和数据都要在最重要的位上先进行。

图1 4-线SPI接口

3.1SPI接口配置

配置时要注意连接MCU的SPI接口必须在主模式下操作。

配置时钟相位时要确保数据的中心在SCLK周期的第一个正边缘处,在选择极性时要确保SCLK在静止状态时为低电平。

图2 SPI接口的时钟相位和极性

3.2SPI接口的时间要求

关于SPI接口的时间要求,详情请查看芯片数据表。

值得注意的是最大SCLK频率(fsclk)是如何改变的,这主要取决于SPI接口的使用情况。

SPI时钟运行的最大频率是10 MHz,在地址字节和数据字节(单字节)之间、地址和数据之间或者每一个数据字节之间(突发访问)的最小延迟是100ns。

如图3所示。

图3 f SCLK = 10 MHz Max

如果各字节之间没有延迟,那么单通道的最大时钟速度是9MHz(图4),突发访问为6.5MHz(图5)。

3.3SPI的访问

芯片上有47个配置寄存器(地址0000至地址0x2E)。

寄存器的读写操作由头地址的R/W 位控制,而burst突发访问位控制访问方式为单字节还是突发访问。

图6 头地址

当CSn变低,我们总是要等到MISO(CHIP_RDYn)变为低电平之后再进行头地址的写操作。

CHIP_RDYn信号表明晶体正在运行,调节数字供给电压是稳定的。

只要芯片不是在SLEEP或XOFF状态或者一个SRES闪光灯发出命令的情况下,SO引脚总是在CSn变成低电平之后也迅速变为低电平。

图7

图7显示了电磁波从IDLE (1)静止状态转变为SLEEP休眠状态(SPWD),接着通过发射一个TX滤波(STX) (2)使其在休眠状态后被唤醒的工作过程。

当CSn变为低电平时电磁波从休眠状态中唤醒。

在CSn首次变为低电平时,MISO变为高电平,然后又立即成为低电平,这样就表示芯片已经准备工作了。

当CSn第二次变为低电平时,因为电磁波回到了休眠状态,所以MISO又变为高电平。

等到电压调节器稳定之后,晶体开始运行,MISO变回低电平,此时可以安全发送TX滤波。

3.4单字节访问

单字节访问寄存器时,突发访问位必须置0。

发送地址头以后可以根据R/W位发送或读入一个数据字节。

在数据字节之后等待一个新的地址,因此,CSn继续保持低电平。

图8表明了数据0x0A是如何首先写入寄存器0x02,然后从同一个寄存器中读出来的。

3.5突发访问

当突发访问位置1时,电磁波会要求一个地址字节和接下来的连续的数据字节,直到CSn 变为高电平,访问终止。

3.6命令滤波

命令滤波是单字节指令,它可以启动一个内部序列(启动RX,进入掉电模式等)。

命令滤波和一系列的状态寄存器(地址0x30到地址0x3F)共享地址。

这些状态寄存器不能用突发访问模式来访问。

如果突发访问位是1,那么访问的就是状态寄存器;如果突发访问位是0,则发送一个命令滤波。

一个命令滤波可能在任何其他SPI访问之后,而不需要将CSn拉至高电平。

在处理完一个SRES命令滤波之后,当MISO引脚变成低电平时,可以处理下一个命令滤波。

命令滤波可以立即被执行,但是当CSn为高电平时SPWD和SXOFF滤波是例外。

当CSn被拉为低电平时,MISO已经变为低电平,表明芯片已经准备好了。

SIDLE(离开RX/TX)滤波紧随在一个寄存器写操作和一个无需等待CHIP_RDYn信号的SRES(重启芯片)滤波后。

在复位滤波之后,在MISO变为低电平之前需要一些时间才能读寄存器0x00。

从这个寄存器读到的数值是0x29(复位之后的默认数值)。

4芯片的状态字节

当在SPI接口上发送头字节、数据字节或命令滤波时,CC1100在SO引脚上发送芯片状

表1 状态字节概要

当写寄存器时,每次一个头字节或者数据字节在MOSI 引脚上传送,一个状态字节都在MISO 引脚上传送。

当读寄存器时,每次一个头字节在 MOSI 引脚上传送时,一个状态字节都在MISO引脚上传送。

注意状态字节的4LSB(FIFO_BYTES_AVAILABLE)可以为TX FIFO (R/W = 0) or和RX FIFO (R/W = 1)提供信息。

图11 状态字节说明

第一次转移是将0x0A写到寄存器0x02上。

因为这是一个写操作,所以当地址头(1)和数据字节(2)都传送时,状态字节在MISO线上传送。

状态字节(0x0F)告诉我们,电磁波处于空闲状态,并且TX FIFO (FIFO_BYTES_AVAILABLE = 15)上有15个或以上的自由字节。

第二次转移是从寄存器0x02上进行读操作。

因为这是一个读操作,所以仅仅在传送地址头时状态字节才能在MISO线上传送。

在MISO线上的下一个字节是寄存器0x02的内容——0x0A。

这个状态字节告诉我们电磁波处在空闲状态(STATE = 0),并且在RX FIFO(FIFO_BYTES_AVAILABLE = 0)上没有字节可用。

5复位

当电源电压满足在数据表中详细列出的需求时,相应的上电复位功能就可以保证。

否则,认为芯片处于一个未知状态,直到一个执行SW复位(见图12)。

•选通低/高电平

•相对于把CSn拉低之后,保持CSn高电平至少40μs

•将CSn拉低以等待SO变为低电平

•在SI线上执行SRES滤波

图12 通过SRES的上电复位

看下面的代码:

6总说明。