Altera_FPGA的特殊管脚的连接(中文)

alterafpga配置

alterafpga配置配置是连接FPGA软件设计到硬件功能实现的桥梁,配置电路部分有误,配置文件无法下载到配置器件中,对FPGA编程,则再好的设计都是浮云。

上电后,配置数据保存在配置RAM中,将配置数据载入配置RAM即是对FPGA编程。

配置方式有很多种,主要区别为FPGA所处的地位和打入数据的方式不同,其基本时序基本相同。

基本时序波形如下:配置过程主要由nCONFIG、nSTATUS、CONF_DONE以及可选的INIT_DONE四个状态信号控制。

一个器件完整的配置过程包括上电复位、配置、初始化三个阶段。

正常上电后,nCONFIG管脚被拉低,器件复位,此时配置RAM的所有内容被清空,所有I/O处于高阻态,其余三个状态信号亦均被拉低,复位结束后,FPGA释放nCONFIG管脚,使其被外部上拉电阻拉高,FPGA在nCONFIG检测到由低到高的跳变沿,配置开始,同时FPGA 采样MSEL的信号状态,决定接受何种配置模式。

随后,FPGA释放nSTATUS管脚,外不上拉电阻将其拉高,FPGA在nSTATUS管脚检测到由低到高的跳变沿,表示FPGA开始接受数据。

配置数据由DATA管脚打入,配置时钟经DCLK管脚送入(被动方式下,主动方式DCLK 由FPGA提供),配置数据在上升沿锁存至FPGA中,配置数据全部打入到FPGA后,FPGA释放CONF_DONE管脚,使其由外部上拉电阻拉高,说明配置结束,进入初始化过程。

INIT_DONE是一个可选的指示初始化完成的信号(Device-Pin&Options-general),INIT_DONE在nCONFIG信号为低或配置的初期时为高电平,而当使能INIT_DONE的比特位(在配置数据的第一帧中)被配置进FPGA后,INIT_DONE信号变低,因此INIT_DONE信号由高到低的跳变表示FPGA配置真正开始,开始接收配置数据,如果INIT_DONE一直保持为高,说明FPGA没有接收到正确配置数据的文件头。

Altera公司FPGA的配置

•

针对FPGA器件不同的内部结构,Altera公司

提供了不同的器件配置方式。Altera FPGA的配

置可通过编程器、JATG接口在线编程及Altera在

线配置等方式进行。

•

Altera器件编程下载电缆的有:

ByteBlaster并行下载电缆,ByteBlasterMV并行

MAX9000(包括MAX9000A)、MAX7000S和MAX7000A

进行编程。ByteBlaster为FPGA提供了一种快速而

廉价的配置方法,设计人员的设计可以直接通过

ByteBlaster下载电缆下载到芯片中去。

(1)下载模式

ByteBlaster并行下载电缆提供两种下载模式: • ①Passive serial mode(PS,被动串行模式)

1. PS(被动串行)模式

•

在PS(被动串行)模式下,MasterBlaster

下载电缆和ByteBlasterMV下载电缆可以对单个

与多个APEXⅡ、APEX20K、Mercury、ACEX1K、

FLEX10K或 FLEX6000系列器件进行配置。在PS模

式,配置数据从数据源通过MasterBlaster下载

电缆和ByteBlasterMV下载电缆串行地传送到器

件,配置数据由数据源提供的时钟同步。

(1)PS模式单个器件的配置电路设计

•

PS模式可以完成对单个APEXⅡ、 NhomakorabeaPEX20K、

Mercury、ACEX1K、FLEX10K或 FLEX6000系列器件

的配置,配置电路如图6.2所示。

•

图中:除 APEX20KE、APEX20KC系列器件外,

Altera FPGA配置及升级

Altera FPGA配置方式及升级方式(针对cyclone II器件)1、配置cyclone II FPGA对于altera fpga,主要配置方式为AS,PS,JTAG三种配置方式。

这几种配置方式在于电路上对器件配置方式引脚选择不同:如图1.1所示:图1.1注意1:对于快速AS模式,只支持配置芯片EPCS16,EPCS64;2:对于JTAG配置模式,只应用JTAG,该引脚连接到地;2、配置器件(图2.1):图2.13、FPGA配置方式具体分体3.1AS(Active Serial)配置:3.1.1原理AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone器件处于主动地位,配置器件处于从属地位。

AS配置器件采用四引脚接口处理:DCLK、DATA、ASDI、nCS;配置数据通过DATA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

3.1.2电路连接方式(图3.1)图3.13.1.3配置时序(图3.2)图3.2在配置完成后到初始化完成所需要299个时钟周期(100M)3.1.4配置文件.pof .jic .rbf3.2PS(Passive Serial)配置方式3.2.1配置原理主动串行配置方式可以通过altera配置器件,一个下载电缆,或者通过一个主控制器,诸如MAX II器件、MCU等来配置FPGA。

配置数据通过DATA0在每个DCLK的上升沿送入器件。

FPGA配置方式选择引脚配置如图3.3所示图3.33.2.2电路连接:配置器件配置(图3.4)图3.4MAX II配置,图3.5图3.5MCU配置,图3.6图图3.63.2.3配置时序图3.73.2.4配置文件格式.rbf .hex .ttf3.3JTAG配置方式3.3.1原理对于cyclone II器件来说,JTAG配置方式优先于其他器件配置方式。

fpga配特殊引脚的含义(FPGAwiththemeaningofaspecialpin)

fpga配特殊引脚的含义(FPGA with the meaning of a special pin)FPGA with the meaning of a special pin1.I/O, ASDOIn AS mode, it is dedicated output pin, and can be used as I/O pin in PS and JTAG mode. In AS mode, this pin is the CII pin that sends the control signal to the serial configuration chip. Also used to read configuration data from the configuration chip. In AS mode, the ASDO has an internal pullup resistor, which has been in effect until the configuration is completed, and the pin becomes a three state input pin. The ASDO pin is connected directly to the ASDI pin (fifth feet) of the configuration chip.2.I/O, nCSOIn AS mode, it is a dedicated output pin that can be used as the I/O pin in PS and JTAG mode. In AS mode, this pin is used by the CII to send the enable pins to the outside serial configuration chip. In AS mode, the ASDO has an internal pullup resistor that has been in effect. This pin is active low. The /CS pin (first feet) is directly connected to the configuration chip.3.I/O, CRC_ERRORWhen the error detection CRC circuit is selected, this foot is used as the CRC_ERROR pin, and if not used by default, it is used as I/O. Note, however, that this pin does not support open drain and reverse. When it is used as CRC_ERROR, the high leveloutput indicates a CRC checksum error (when an individual bit of the SRAM is configured). CRC circuit support can be added to the setting. This foot is usually used with the nCONFIG foot. That is, if the configuration process is wrong, reconfigure it4.I/O, CLKUSRWhen the Enable User-supplled start-up clock (CLKUSR) option is opened in the software, this pin can only be used as an initialization clock input for the user. In all configuration data have been received, CONF_DONE pin will become a high level, the CII device 299 clock cycles are needed to initialize the I/O register, FPGA and so on, there are two ways, one is using the internal oscillator (10MHz), another is from CLKUSR in the clock (maximum not more than 100MHz). This feature can delay the time FPGA starts working and can be used in special applications that require synchronization with other devices.5.I/O, VREFUsed to provide a reference level for certain differential standards. If not used, you can use it as a I/O.6. DATA0Dedicated input pin. In AS mode, the configuration process is: CII sets the nCSO low, and the configured chip is enabled. CII then cooperates with DCLK and ASDO to send commands and read addresses to the configuration chip. Configure the chip and then send the data to the CII via the DATA pin. The DATA foot is attached to the CII's DATA0 foot. After all configurationdata is received by the CII, the CONF_DONE pin is released (that is, the CONF_DONE pin is not forced low) and the CONF_DONE pin is open drain (Open-Drain). At this point, the 10K will turn on a high level because the CONF_DONE will pick up a resistor on the outside. At the same time, the CII stops the DCLK signal. After the CONF_DONE becomes high (when it becomes equivalent to an input pin), the initialization process begins. So, CONF_DONE must have a 10K resistor on the outside of the foot to ensure that the initialization process starts correctly. DATA0, DCLK, NCSO, and ASDO have weak pullup resistors on their feet, and they are always valid. Upon completion of the configuration, these pins are turned into an input three state, and the level is set to a high level by an internal pullup resistor. In AS mode, the DATA0 receives the DATA (second pin) of the configuration chip.7. DCLKPS mode is input, AS mode is output. In PS mode, the DCLK is a clock input pin that is the clock that the external device sends the configuration data to the FPGA. Data is placed on the rising edge of the DCLK to data in AS mode, and the DCLK pin is a clock output pin that is configured to provide a clock. Connect directly to the DCLK pin of the configuration chip (sixth feet). No matter what configuration mode, after the configuration is completed, this foot will become three states. If an external configuration device is attached, the configuration device will set the DCLK pin to low level. If you are using the master chip, you can either set the DCLK high or you can lower the DCLK. When the configuration is complete, triggering this pin does not affect the configured FPGA. Thispin has an input Buffer that supports the hysteresis function of the Schmidt flip-flop.8. nCEDedicated input pin. This pin is an active low chip enable signal. The nCE pin is configured to enable the foot. In configuration, initialization, and user mode, the nCE pin must be set low. In the configuration of multiple devices, the nCE pin of the first device is set low, and its nCEO is connected to the nCE pin of the next device, forming a chain. The nCE pin also requires a low nCE foot in the JTAG programming mode.This pin has an input Buffer that supports the hysteresis function of the Schmidt flip-flop.9. nCONFIGDedicated input pins. This pin is a configuration control input pin. If this foot is low in user mode, the FPGA loses its configuration data and goes into a reset state and sets all the I/O feet into three states. The process of changing nCONFIG from low level to high level will initialize the reconfiguration process. If the configuration scheme uses an enhanced configuration device or EPC2, the user can connect the nCONFIG pin directly to the VCC or to the nINIT_CONF pin of the configuration chip. This pin has an input Buffer that supports the hysteresis function of the Schmidt flip-flop. In fact, in user mode, the nCONFIG signal is used to initialize the reconfiguration. When the nCONFIG foot is low, the initialization process begins. When the nCONFIG pin is low, theCII is reset and goes into the reset state. The nSTATUS and CONF_DONE pins are set low and all the I/O pins are in the three state. The nCONFIG signal must remain at least 2us. When nCONFIG returns to the high level state, the nSTATUS is released again. The reconfiguration starts. In actual application, the nCONFIG pin can be connected with a pull-up resistor of 10K to 3.3V.10. DEV_OEI/O pin or global I/O enable pin. In the Quartus II software can enable the DEV_OE option (Enable Device-wideoutput Enable), if can make this a function, this pin can be enabled when the global I/O feet, this foot function is, if it is set low, all I/O into three states.11. INIT_DONEI/O pin or drain open output pin. When this foot is enabled, the foot jumps from low to high, indicating that the FPGA has entered the user mode. If the INIT_DONE output pin is enabled, this pin cannot be used as user I/O after configuration is complete. Inside the QuartusII, this pin can be enabled by enabling the Enable INIT_DONE output option.12. nCEOI/O pin or output pin. When the configuration is complete, this pin outputs low level. In the configuration of multiple devices, this pin will connect to the next device's nCE pin. This time, it also needs a 10K pull-up resistor outside to Vccio. The configuration process of multiple devices, finally a nCEOdevice can float. If you want to use this pin as an available I/O, you need to set it up inside the software. In addition, even if the I/O, but also after the completion of the configuration.13. nSTATUSThis is a dedicated configuration status pin. Two way foot, when it is the output pin, is open drain. After power on, the FPGA immediately sets the nSTATUS foot low and releases it after power on reset (POR) and sets it high. As a status output pin, if any error occurs during configuration, the nSTATUS pin is lowered. As the status input pin, during the configuration or initialization, the external control chip can pull this pin down, and FPGA will enter the wrong state at this time. This foot can not be used as an ordinary I/O foot. The nSTATUS pin must be pulled up by a 10K ohm resistor.14. CONF_DONEThis is a dedicated configuration status pin. Two way foot, when it is the output pin, is open drain. When it is used as a status output pin, it is set low before and during configuration. Once the configuration data is received and no errors are made, the CONF_DONE will be released at the start of the initialization cycle. When used as a status input pin, after all data has been received, it should be set to a high level. After that, the device starts initialization and goes into user mode. It should not be used as a regular I/O. The outside of the foot must also be connected with a 10K ohm resistor.15. MSEL[1:0]These pins should be connected to zero or power, indicating high or low level. 00 with AS mode, 10 PS mode, AS mode is 01 FAST. If in JTAG mode, it with their 00 JTAG mode and the MSEL has nothing to do with JTAG mode, MSEL will be ignored, but because they can not float, so suggest that it be received.16 DEV_CLRnI/O or global clear input. In QuartusII, if you choose the Enable Device-Wide Reset (DEV_CLRn) this function. This pin is the global reset. When this pin is low, all registers are cleared. This pin does not affect the JTAG's boundary scan or programming operations.Application of FPGA configuration pinFor FPGA applications, you need to know the following points.The nCONFIG, nSTATUS, and CONF_DONE require the pull-up resistor of the 10K, and the nCE requires a 10K pull-down resistor;NCONFIG for configuration control, the dedicated input pin sets the low FPGA to lose data;The nSTATUS is a dedicated bidirectional pin for the FPGA. 0 indicates that the FPGA is in a busy state and is released at 1 after the pull-up, and the FPGA begins to be in configuration.CONF_DONE dedicated configuration, two-way feet, FPGA configuration is 0, after the configuration is released, the role of the external pull-up is 1. NCE configuration enables dedicated input pins. In configuration, initialization, and user mode, the nCE pin must be set low.MSEL configure pin for mode;TDI, TMS, 10K pull-up resistor, TCK, 10K pull-down resistor, for JTAG;ASDO, nCSO, DCLK and DATA0 are used for the communication between FPGA and configuration chip, and there is no pullup on the inside, and no external resistance is needed.The clock pin can only be input and cannot be output.6 、 pull / pull resistance:1) ensure that the initial values of the circuit. For example, TCK signal using a pull-down resistor. Why the pull-down resistor instead of the pull-up resistor? Because pull-down resistor makes the initial value of the TCK signal is 0, because it is a clock signal, can guarantee the clock signal in the initial value after the first rise along the edge, and the JTAG control of resistance it is on the rising edge of TCK to write configuration data within the FPGA.2) here / pull-down resistor only belongs to the recommended value, determine the value is not, the purpose is to ensure the quality of the signal. The resistance as an example, if thepull-up resistor is above 10K, the pin has an equivalent capacitance to ground, because T=RC, C by the device process, the greater the resistance, charge and discharge the longer the time, the rising edge of the slower signal, the slope is small. The rise time if more than JTAG control circuit requirements to write data within the FPGA may be wrong. So, if the pull-up resistor smaller? Will rise time smaller? Yes. Resistance decreases, rise time small, the slope becomes larger, but also brought a serious problem, if the resistance is small to a certain extent, the signal will be at the rising edge of the emergence of the red signal ringing phenomenon, will seriously. If the resistance is too small, the intrusion tolerance over current devices IO, JTAG control circuit Will burn out. So, what is the resistance to meet the general requirements of PCB using 4.7K. in general?3) to ensure the driving ability of signal. As mentioned earlier, the resistance is small, the signal slope is small, and the driving force of signals is stronger. The more resistance signal slope is bigger, and the driving force of signals is weak. This point in the JTAG daisy chain circuit and its important。

Altera公司FPGA的配置

10

(4)PCB电路板上的10针连接插头

PCB板上的10针插头连接到FPGA器件的编程 或配置引脚上,ByteBlaster下载电缆的10针插座 连接到PCB板上的10针插头,ByteBlaster电缆通 过10针插头获得电源并下载数据到FPGA器件上。

编辑ppt

11

2. ByteBlasterMV并行下载电缆

编辑ppt

4

(2)电缆插头与插座

ByteBlaster与PC机并口相连的是25针插头,与FPGA 应用电路PCB电路板相连的是10针插座。编程数据从PC机 并口通过ByteBlaster电缆下载到电路板。连接示意图如 图6.1所示。

注意:利用 ByteBlaster下载电缆配置/编程3.3V器 件(如FLEX10KA、MAX7000A器件)时,要将电缆的VCC脚 连到5.0V电源,而器件的VCC脚连到3.3V电源。FLEX10KA 和 MAX7000A器件能够耐压到 5.0V,因此,ByteBlaster 电缆的5.0 V输出不会对 3.3 V器件造成损害,但5.0V电 源中应连接上拉电阻。

编辑ppt

15

(3)电缆插头与插座

ByteBlasterMV的25针插头,与ByteBlaster 下载电缆的区别仅是第15脚不同,ByteBlaster 连到GND,而ByteBlasterMV连到VCC。

ByteBlasterMV的10针插座与ByteBlaster电 缆的10针插座完缆

针对FPGA器件不同的内部结构,Altera公司 提供了不同的器件配置方式。Altera FPGA的配 置可通过编程器、JATG接口在线编程及Altera在 线配置等方式进行。

Altera器件编程下载电缆的有: ByteBlaster并行下载电缆,ByteBlasterMV并行 下载电缆,MasterBlaster串行/USB通信电缆, BitBlaster串口下载电缆。

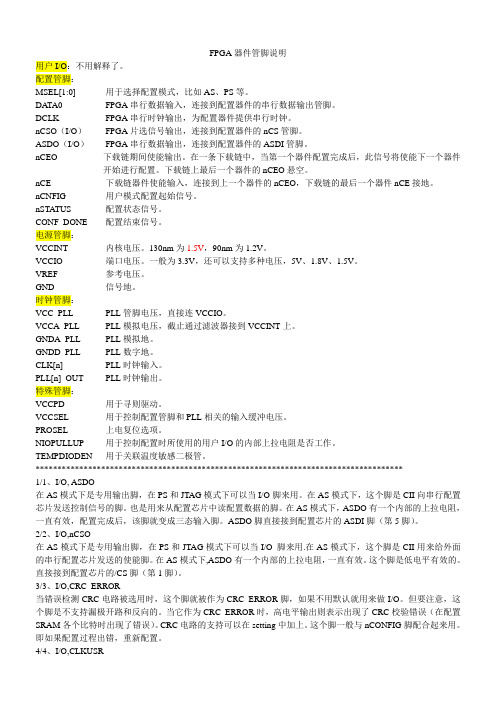

FPGA器件管脚说明

FPGA器件管脚说明用户I/O:不用解释了。

配置管脚:MSEL[1:0] 用于选择配置模式,比如AS、PS等。

DA TA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。

DCLK FPGA串行时钟输出,为配置器件提供串行时钟。

nCSO(I/O)FPGA片选信号输出,连接到配置器件的nCS管脚。

ASDO(I/O)FPGA串行数据输出,连接到配置器件的ASDI管脚。

nCEO 下载链期间使能输出。

在一条下载链中,当第一个器件配置完成后,此信号将使能下一个器件开始进行配置。

下载链上最后一个器件的nCEO悬空。

nCE 下载链器件使能输入,连接到上一个器件的nCEO,下载链的最后一个器件nCE接地。

nCNFIG 用户模式配置起始信号。

nSTATUS 配置状态信号。

CONF_DONE 配置结束信号。

电源管脚:VCCINT 内核电压。

130nm为1.5V,90nm为1.2V。

VCCIO 端口电压。

一般为3.3V,还可以支持多种电压,5V、1.8V、1.5V。

VREF 参考电压。

GND 信号地。

时钟管脚:VCC_PLL PLL管脚电压,直接连VCCIO。

VCCA_PLL PLL模拟电压,截止通过滤波器接到VCCINT上。

GNDA_PLL PLL模拟地。

GNDD_PLL PLL数字地。

CLK[n] PLL时钟输入。

PLL[n]_OUT PLL时钟输出。

特殊管脚:VCCPD 用于寻则驱动。

VCCSEL 用于控制配置管脚和PLL相关的输入缓冲电压。

PROSEL 上电复位选项。

NIOPULLUP 用于控制配置时所使用的用户I/O的内部上拉电阻是否工作。

TEMPDIODEN 用于关联温度敏感二极管。

************************************************************************************1/1、I/O, ASDO在AS模式下是专用输出脚,在PS和JTAG模式下可以当I/O脚来用。

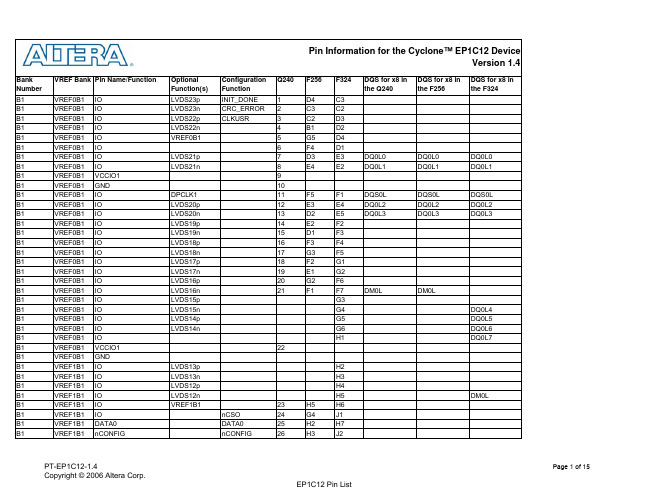

altera公司cyclone fpga管脚分配

Pin NamePin Type (1st, 2nd, &3rd Function)Pin DescriptionVCCIO[1..4]Power These are I/O supply voltage pins for banks 1 through 4. Each bank can support a different voltage level. VCCIO supplies power to the output buffers for all I/O standards. VCCIO also supplies power to the input buffers used for the LVTTL, LVCMOS, 1.5-V, 1.8-V, 2.5-V, and 3.3-V PCI I/O standards.VCCINT Power These are internal logic array voltage supply pins. VCCINT also supplies power to the input buffers used for the LVDS, SSTL2, and SSTL3 I/O standards.GNDGroundDevice ground pins. All GND pins should be connected to the board GND plane.VREF[0..2]B[1..4]I/O, Input Input reference voltage for banks 1-4. If a bank uses a voltage-referenced I/O standard, then these pins are used as the voltage-reference pins for the bank. If voltage reference I/O standards are not used in the bank, the VREF pins are available as user I/O pins.VCCA_PLL[1..2]Power Analog power for PLLs[1..2]. The designer must connect this pin to 1.5 V, even if the PLL is not used.GNDA_PLL[1..2]Ground Analog ground for PLLs[1..2]. The designer can connect this pin to the GND plane on the board.GNDG_PLL[1..2]Ground Guard ring ground for PLLs[1..2]. The designer can connect this pin to the GND plane on the board.NCNo Connect No connect pins should not be connected on the board. They should be left floating.CONF_DONE Bidirectional (open-drain)This is a dedicated configuration status pin; it is not available as a user I/O pin.nSTATUS Bidirectional (open-drain)This is a dedicated configuration status pin; it is not available as a user I/O pin.nCONFIGInputDedicated configuration control input. A low transition resets the target device; a low-to-high transition begins configuration. All I/O pins tri-state when nCONFIG is driven low.DCLK Input (PS mode), Output (AS mode)In passive serial configuration mode, DCLK is a clock input used to clock configuration data from an external source into the Cyclone device. In active serial configuration mode, DCLK is a clock outputfrom the Cyclone device (the Cyclone device acts as master in this mode). This is a dedicated pinused for configuration.DATA0InputDedicated configuration data input pin.nCE Input Active-low chip enable. Dedicated chip enable input used to detect which device is active in a chain of devices. When nCE is low, the device is enabled. When nCE is high, the device is disabled.nCEOOutputOutput that drives low when device configuration is complete. During multi-device configuration, this pin feeds a subsequent device’s nCE pin.ASDO I/O, OutputActive serial data output from the Cyclone device. This output pin is utilized during active serial configuration mode. The Cyclone device controls configuration and drives address and control information out on ASDO. In passive serial configuration, this pin is available as a user I/O pin.nCSO I/O, OutputChip select output that enables/disables a serial configuration device. This output is utilized during active serial configuration mode. The Cyclone device controls configuration and enables the serial configuration device by driving nCSO low. In passive serial configuration, this pin is available as a user I/O pin.CRC_ERRORI/O, OutputActive high signal that indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled.INIT_DONE I/O, Output (open-drain)This is a dual-purpose pin and can be used as an I/O pin when not enabled as INIT_DONE. When enabled, the pin indicates when the device has entered user mode. This pin can be used as a user I/Opin after configuration.CLKUSRI/O, InputOptional user-supplied clock input. Synchronizes the initialization of one or more devices. This pin can be used as a user I/O pin after configuration.DEV_CLRn I/O, InputDual-purpose pin that can override all clears on all device registers. When this pin is driven low, all registers are cleared; when this pin is driven high, all registers behave as defined in the design.DEV_OE I/O, Input Dual-purpose pin that can override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated; when this pin is driven high, all I/O pins behave as defined in the design.MSEL[1..0]Input Dedicated mode select control pins that set the configuration mode for the device.TMS Input This is a dedicated JTAG input pin.TDI Input This is a dedicated JTAG input pin.TCK Input This is a dedicated JTAG input pin.TDO OutputThis is a dedicated JTAG output pin.CLK0Input, LVDS Input Dedicated global clock input. The dual-function of CLK0 is LVDSCLK1p, which is used for differential input to PLL1.CLK1Input, LVDS Input Dedicated global clock input. The dual-function of CLK1 is LVDSCLK1n, which is used for differential input to PLL1.CLK2Input, LVDS Input Dedicated global clock input. The dual-function of CLK2 is LVDSCLK2p, which is used for differential input to PLL2.CLK3Input, LVDS InputDedicated global clock input. The dual-function of CLK3 is LVDSCLK2n, which is used for differential input to PLL2.Configuration and JTAG Pins Pin Information for the Cyclone™ EP1C12 DeviceVersion 1.4Supply and Reference PinsClock and PLL PinsPT-EP1C12-1.4Copyright © 2006 Altera Corp.Pin DefinitionsPage 12 of 15Pin NamePin Type (1st, 2nd, & 3rd Function)Pin DescriptionPin Information for the Cyclone™ EP1C12 DeviceVersion 1.4DPCLK[7..0]I/O Dual-purpose clock pins that can connect to the global clock network. These pins can be used forhigh fan-out control signals, such as clocks, clears, IRDY, TRDY, or DQS signals. These pins are also available as user I/O pins.PLL1_OUTp I/O, Output External clock output from PLL 1. This pin can be used with differential or single ended I/O standards. If clock output from PLL1 is not used, this pin is available as a user I/O pin.PLL1_OUTn I/O, Output Negative terminal for external clock output from PLL1. If the clock output is single ended, this pin is available as a user I/O pin.PLL2_OUTp I/O, Output External clock output from PLL 2. This pin can be used with differential or single ended I/O standards. If clock output from PLL2 is not used, this pin is available as a user I/O pin.PLL2_OUTnI/O, OutputNegative terminal for external clock output from PLL2. If the clock output is single ended, this pin is available as a user I/O pin.LVDS[0..102]p I/O, LVDS RX or TXDual-purpose LVDS I/O channels 0 to 102. These channels can be used for receiving or transmitting LVDS compatible signals. Pins with a "p" suffix carry the positive signal for the differential channel. If not used for LVDS interfacing, these pins are available as user I/O pins.LVDS[0..102]n I/O, LVDS RX or TX Dual-purpose LVDS I/O channels 0 to 102. These channels can be used for receiving or transmitting LVDS compatible signals. Pins with an "n" suffix carry the negative signal for the differential channel. If not used for LVDS interfacing, these pins are available as user I/O pins.LVDSCLK1p Input, LVDS Input Dual-purpose LVDS clock input to PLL1. If differential input to PLL1 is not required, this pin is available as the CLK0 input pin.LVDSCLK1n Input, LVDS Input Dual-purpose LVDS clock input to PLL1. If differential input to PLL1 is not required, this pin is available as the CLK1 input pin.LVDSCLK2p Input, LVDS Input Dual-purpose LVDS clock input to PLL2. If differential input to PLL2 is not required, this pin is available as the CLK2 input pin.LVDSCLK2nInput, LVDS InputDual-purpose LVDS clock input to PLL2. If differential input to PLL2 is not required, this pin is available as the CLK3 input pin.DQS[0..1][L,R,T,B]I/O Optional data strobe signal for use in external memory interfacing. These pins also function as DPCLK pins; therefore, the DQS signals can connect to the global clock network. A programmable delay chain is used to shift the DQS signals by 90 or 72 degrees.DQ[0..7][L,R,T,B]I/O Optional data signal for use in external memory interfacing.DM[0..1][L,R,T,B]I/OOptional data mask output signal for use in external memory interfacing.Dual-Purpose LVDS & External Memory Interface PinsPT-EP1C12-1.4Copyright © 2006 Altera Corp.Pin DefinitionsPage 13 of 15Pin Information for the Cyclone™ EP1C12 Device, ver 1.4VREF2B2VREF1B2VREF0B2B2V R E F 0B 1B 1B 3V R E F 0B 3V R E F 1B 1V R E F 1B 3PLL1PLL2V R E B 2B 1V R E B 2B 3B4VREF2B4VREF1B4VREF0B4Notes:1.This is a top view of the silicon die.2.This is a pictoral representation only to get an idea of placement on the device. Refer to the pin-list andthe Quartus II for exact locations.PT-EP1C12-1.4Copyright © 2006 Altera Corp.Bank & PLL DiagramPage 14 of 15Pin Information for the Cyclone™ EP1C12 DeviceVersion 1.4Version NumberDate Changes Made1.43/6/2006Added CRC_ERROR pin in Pin List and Pin DefinitionsPT-EP1C12-1.4Copyright © 2006 Altera Corp.Revision HistoryPage 15 of 15。

Altera FPGA特殊管脚连接

如果在配置或初始化过程中,有一个外部的信号源驱动本管脚为低,则器件进入一个错误的状态;

在配置或初始化之后,驱动本管脚为低,不会影响器件。但是,如果使用专用配置器件,驱动本管脚低将引起配置器件试图去配置APEX或FLEX器件。

(详细见AN116中的配置时序)

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

1器件级的清零

2用户I/O

All

输入

此管脚需要在编译设置中设定才能实现第一功能,缺省是第二功能;

当本引脚被拉低,所有寄存器被清除。

当本引脚被拉高,所有寄存器都处于程序控制状态。

TDI

APEX II

APEX 20K

本管脚必须通过一个1K的电阻上拉到VCCIO

(APEX 20KE或APEX 20KC器件使用10K欧姆电阻)

外部的信号源可以驱动本管脚为低,来延迟初始化的过程,当使用一个配置器件进行配置除外,

在配置以及初始化之后,驱动本管脚为低,不影响配置器件。

(详细见AN116中的配置时序)

DCLK

APEX II

nCONFIG

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

特殊管脚不能做用户I/O

All

输入

配置控制引脚:

由0-1的跳变开始配置,由1-0跳变则复位器件;当设定本管脚为0时,所有I/O为三态。

(详细见AN116中的配置时序)

CONF_DONE

APEX II

APEX 20K

FPGA各管脚简介

用户I/O:不用解释了。

配置管脚:MSEL[1:0] 用于选择配置模式,比如AS、PS等。

DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。

DCLK FPGA串行时钟输出,为配置器件提供串行时钟。

nCSO(I/O)FPGA片选信号输出,连接到配置器件的nCS管脚。

ASDO(I/O)FPGA串行数据输出,连接到配置器件的ASDI管脚。

nCEO 下载链期间始能输出。

在一条下载链中,当第一个器件配置完成后,此信号将始能下一个器件开始进行配置。

下载链上最后一个器件的nCEO悬空。

nCE 下载链器件始能输入,连接到上一个器件的nCEO,下载链的最后一个器件nCE接地。

nCNFIG 用户模式配置起始信号。

nSTATUS 配置状态信号。

CONF_DONE 配置结束信号。

电源管脚:VCCINT 内核电压。

130nm为1.5V,90nm为1.2VVCCIO 端口电压。

一般为3.3V,还可以支持多种电压,5V、1.8V、1.5VVREF 参考电压GND 信号地时钟管脚:VCC_PLL PLL管脚电压,直接连VCCIOVCCA_PLL PLL模拟电压,截止通过滤波器接到VCCINT上GNDA_PLL PLL模拟地GNDD_PLL PLL数字地CLK[n] PLL时钟输入PLL[n]_OUT PLL时钟输出特殊管脚:VCCPD 用于寻则驱动VCCSEL 用于控制配置管脚和PLL相关的输入缓冲电压PROSEL 上电复位选项NIOPULLUP 用于控制配置时所使用的用户I/O的内部上拉电阻是否工作TEMPDIODEN 用于关联温度敏感二极管******************************************************************************** ****************************************************1/1.I/O, ASDO在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。

FPGA(ep2c8q208c8n)引脚中文详解

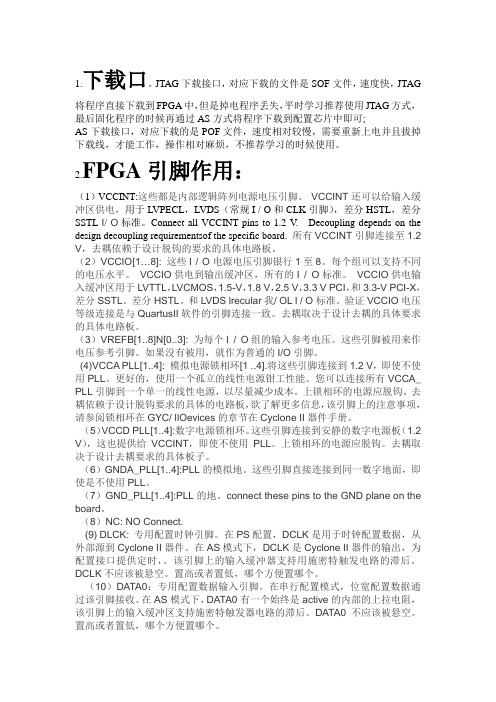

1.下载口。

JTAG下载接口,对应下载的文件是SOF文件,速度快,JTAG 将程序直接下载到FPGA中,但是掉电程序丢失,平时学习推荐使用JTAG方式,最后固化程序的时候再通过AS方式将程序下载到配置芯片中即可;AS下载接口,对应下载的是POF文件,速度相对较慢,需要重新上电并且拔掉下载线,才能工作,操作相对麻烦,不推荐学习的时候使用。

2.FPGA引脚作用:(1)VCCINT:这些都是内部逻辑阵列电源电压引脚。

VCCINT还可以给输入缓冲区供电,用于LVPECL,LVDS(常规I / O和CLK引脚),差分HSTL,差分SSTL I/ O标准。

Connect all VCCINT pins to 1.2 V. Decoupling depends on the design decoupling requirementsof the specific board.所有VCCINT引脚连接至1.2 V,去耦依赖于设计脱钩的要求的具体电路板。

(2)VCCIO[1…8]: 这些I / O电源电压引脚银行1至8。

每个组可以支持不同的电压水平。

VCCIO供电到输出缓冲区,所有的I / O标准。

VCCIO供电输入缓冲区用于LVTTL,LVCMOS,1.5-V,1.8 V,2.5 V,3.3 V PCI,和3.3-V PCI-X,差分SSTL。

差分HSTL。

和LVDS lrecular我/ OL I / O标准。

验证VCCIO电压等级连接是与QuartusII软件的引脚连接一致。

去耦取决于设计去耦的具体要求的具体电路板。

(3)VREFB[1..8]N[0..3]: 为每个I / O组的输入参考电压。

这些引脚被用来作电压参考引脚。

如果没有被用,就作为普通的I/O引脚。

(4)VCCA PLL[1..4]: 模拟电源锁相环[1 ..4].将这些引脚连接到1.2 V,即使不使用PLL。

更好的,使用一个孤立的线性电源钳工性能。

FPGA串行管脚说明

一、被动串行(PS)在做PS配置时,FPGA配置数据从储存器中读出,写入到FPGA的DATA0接口上。

这些存储器是FLASH器件。

数据由DCLK时钟信号管脚的上升沿打入FPGA,每个DCLK时钟周期输入1比特数据。

·DCLK(配置时钟);·DATA0(配置数据);·nCONFIG(配置命令);·nSTATUS(状态信号);·CONF_DONE(配置完成指示)。

在PS方式下,FPGA处于完全被动地位。

FPGA接收配置时钟、配置命令和配置数据,给出配置的状态信号以及配置完成指示信号等。

在配置FPGA时,首先需要将nCONFIG拉低(至少40us),然后拉高。

当nCONFIG 被拉高后,FPGA的nSTATUS也将变高,表示这时已经开始配置,外部电路旧可以用DCLK的时钟上升沿一位一位地将配置数据写入到FPGA中。

当最后一个比特数据写入以后,CONF_DONE管脚被FPGA释放,被外部的上拉电阻拉高,FPGA随即进入初始化状态。

在完成初始化过程后,FPGA正式进入用户模式。

【注】:有的配置芯片没有nINIT_CONF管脚,只需将FPGA的nCONFIG信号弱上拉到Vcc即可。

在上电后,FPGA会在nCONFIG管脚上检测到一个从低到高的跳变沿,因此可以自动启动配置过程。

有三种配置FPGA的方法:1、使用Altera的配置芯片与FPGA相连;2、使用下载电缆通过FPGA的PS口配置;3、使用微处理器配置FPGA。

下图是使用微处理器配置FPGA的示意图:PS:用微处理器配置FPGA【注】:如果外部器件将.rbf文件配置到FPGA中,必须确保配置文件中的最低位先入。

如果比特顺序错误,将导致配置失败。

C代码实现:。

Altera-FPGA管脚弱上拉电阻详细设置方法

Altera FPGA管脚弱上拉电阻的软件设置方法

在使用Altera 的FPGA 时候,由于系统需求,需要在管脚的内部加上上拉电阻。

Quartus II 软件中在Assignment Editor 中可以设置。

具体过程如下:

1、在菜单Assignments 中选择Assignment Editor:

2、在弹出的界面里选择I/O Features:

3、选择assignment name为弱上拉,value为on。

注意:目前自己知道在弱上拉时,value的值为on,value的值会根据assignment name 选择不同而不同,例如下图。

4、查找需要上拉的端口:

经过上面步骤后,如图:

前5步结果:

第6步结果:

1、双击to 下面方框;

2、单击绿色方框内图标;

3、在*前输入相应

的端口名称;

4、单击list

信号显示区

5、选择相应信号

后单击此按钮

6、单击OK

备注:该窗口有助于选择将要上拉的管脚。

5、保存然后再重新编译,设置完成。

在.qsf中可以看到对应的端口已经上拉。

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sw1_n

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sw2_n

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sw3_n。

连接Spansion SPI 串行闪存,以配置Altera FPGA

注: 1. 虽然制造商和器件 ID 不同,但器件具有兼容的针脚、封装、功能和命令集。

2. 针对这一系列器件, Spansion 可以提供其它封装形式。

图 4.2 Spansion SPI 串行闪存与 Cyclone III/IV FPGA 配置连接

䖲SPI 䮾ᄬ ㋏㒳ݙ㓪(ISP)

ᓣ 䗝ᢽ (SPI)

2012 年 3 月 12

Configuring_Altera_FPGAs_via_SPI_Flash_AN_05

3

应用说明

表 4.14 中列出了每个 Altera FPGA 系列的模式选择 (MSEL) 针脚的逻辑电平和电压连接。模式选择针脚具有 始终有效的内部下拉电阻。

表 4.5 到表 4.11 介绍了 Cyclone、 Stratix 和 Arria 系列不同成员典型配置位要求所需的最小 SPI 闪存器件。

配置位数目 (1)

2,944,088 2,944,088 4,086,848 5,748,552 9,534,304 9,534,304 14,889,560 19,965,752 28,571,696

最小 SPI 闪存器件 (Spansion 部件号) (2)

S25FL004K S25FL004K S25FL004K S25FL008K S25FL016K S25FL016K S25FL016K S25FL032P S25FL032P

由 FPGA 器件生成的串行时钟 (DCLK) 控制着从 SPI 闪存到 FPGA 的配置数据传输。所有配置数据都传输到 FPGA 之后,FPGA 会释放由外部拉升电阻拉高的 CONF_DONE 针脚。CONF_DONE 变为逻辑高电平之后, 会开始 FPGA 初始化。内部初始化之后, FPGA 会进入用户模式。

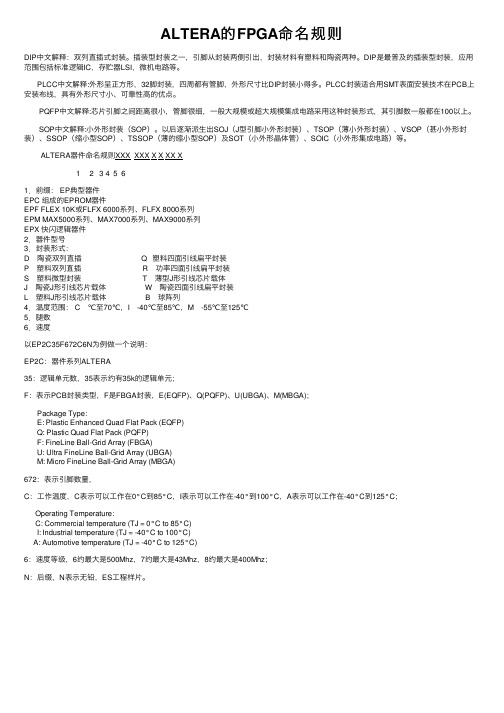

ALTERA的FPGA命名规则

ALTERA的FPGA命名规则DIP中⽂解释:双列直插式封装。

插装型封装之⼀,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DIP是最普及的插装型封装,应⽤范围包括标准逻辑IC,存贮器LSI,微机电路等。

PLCC中⽂解释:外形呈正⽅形,32脚封装,四周都有管脚,外形尺⼨⽐DIP封装⼩得多。

PLCC封装适合⽤SMT表⾯安装技术在PCB上安装布线,具有外形尺⼨⼩、可靠性⾼的优点。

PQFP中⽂解释:芯⽚引脚之间距离很⼩,管脚很细,⼀般⼤规模或超⼤规模集成电路采⽤这种封装形式,其引脚数⼀般都在100以上。

SOP中⽂解释:⼩外形封装(SOP)。

以后逐渐派⽣出SOJ(J型引脚⼩外形封装)、TSOP(薄⼩外形封装)、VSOP(甚⼩外形封装)、SSOP(缩⼩型SOP)、TSSOP(薄的缩⼩型SOP)及SOT(⼩外形晶体管)、SOIC(⼩外形集成电路)等。

ALTERA器件命名规则XXX XXX X X XX X1 2 3 4 5 61.前缀: EP典型器件EPC 组成的EPROM器件EPF FLEX 10K或FLFX 6000系列、FLFX 8000系列EPM MAX5000系列、MAX7000系列、MAX9000系列EPX 快闪逻辑器件2.器件型号3.封装形式:D 陶瓷双列直插 Q 塑料四⾯引线扁平封装P 塑料双列直插 R 功率四⾯引线扁平封装S 塑料微型封装 T 薄型J形引线芯⽚载体J 陶瓷J形引线芯⽚载体 W 陶瓷四⾯引线扁平封装L 塑料J形引线芯⽚载体 B 球阵列4.温度范围: C ℃⾄70℃,I -40℃⾄85℃,M -55℃⾄125℃ 5.腿数6.速度以EP2C35F672C6N为例做⼀个说明:EP2C:器件系列ALTERA35:逻辑单元数,35表⽰约有35k的逻辑单元;F:表⽰PCB封装类型,F是FBGA封装,E(EQFP)、Q(PQFP)、U(UBGA)、M(MBGA);Package Type:E: Plastic Enhanced Quad Flat Pack (EQFP)Q: Plastic Quad Flat Pack (PQFP)F: FineLine Ball-Grid Array (FBGA)U: Ultra FineLine Ball-Grid Array (UBGA)M: Micro FineLine Ball-Grid Array (MBGA)672:表⽰引脚数量,C:⼯作温度,C表⽰可以⼯作在0°C到85°C,I表⽰可以⼯作在-40°到100°C,A表⽰可以⼯作在-40°C到125°C;Operating Temperature:C: Commercial temperature (TJ = 0°C to 85°C)I: Industrial temperature (TJ = -40°C to 100°C)A: Automotive temperature (TJ = -40°C to 125°C)6:速度等级,6约最⼤是500Mhz,7约最⼤是43Mhz,8约最⼤是400Mhz;N:后缀,N表⽰⽆铅,ES⼯程样⽚。

ALTERA FPGA 配置接口

ALTERA FPGA 配置接口标准JTAG接口:标准AS接口:标准PS接口:USB Blaster 功能概述∙支持ALTERA 公司全系列FPGA/CPLD器件∙支持ALTERA公司全系列主动串行配置器件∙支持ALTERA公司全系列增强配置器件∙支持AS﹑PS﹑JTAG三种下载模式∙高速、稳定,内部采用FT245R+CPLD设计∙支持1.2-5V编程电压∙支持SignalTap II 嵌入式逻辑分析仪∙支持Nios II嵌入式处理器的通信和调试支持的软件∙Quartus II集成开发环境∙NIOS II IDE 集成开发环境∙NIOS II EDS集成开发环境支持的器件∙CPLD:MAX3000、MAX7000A/B/S、MAX9000 和MAX II 等∙FPGA:Stratix、Stratix II、Cyclone、Cyclone II、CycloneIII、ACEX 1K、APEX 20K 和FLEX 10K 等∙主动串行配置器件:EPCS1、EPCS4、EPCS16等∙增强配置器件:EPC1、EPC4 等产品特性∙采用高速下载方案:FT245+CPLD+244,下载速度接近原厂ALTERA USB BLASTER 相比其它下载方案,如68013或C8051F等方案,速度快1-3倍与PC机的连接∙通过USB 2.0接口与计算机连接与目标板的连接∙通过JTAG、AS、PS接口与目标板连接硬件开发环境通过USB Blaster连接“FPGA/CPLD目标板”和“PC”,建立完整的硬件开发环境,对目标芯片进行编程、调试连接目标板USB Blaster可以通过三种接口连接至目标板JTAG、AS、PS接口是如何定义的?(点击查看)请注意,VCC和GND切勿接反,以免烧坏USB BlasterUSB Blaster状态灯说明∙红灯:电源灯∙绿灯:信号指示灯,进行软件下载时,绿灯亮配置清单1. USB Blaster编程器× 12. USB数据线× 13. 10-pin线× 14. 资料光盘× 1。

Altera_FPGA特殊管脚

用户I/O:通用输入输出引脚。

配置管脚:MSEL[1:0] 用于选择配置模式,比如AS、PS等。

DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。

DCLK FPGA串行时钟输出,为配置器件提供串行时钟。

nCSO(I/O)FPGA片选信号输出,连接到配置器件的nCS管脚。

ASDO(I/O)FPGA串行数据输出,连接到配置器件的ASDI管脚。

nCEO 下载链期间始能输出。

在一条下载链中,当第一个器件配置完成后,此信号将始能下一个器件开始进行配置。

下载链上最后一个器件的nCEO悬空。

nCE 下载链器件始能输入,连接到上一个器件的nCEO,下载链的最后一个器件nCE接地。

nCNFIG 用户模式配置起始信号。

nSTATUS 配置状态信号。

CONF_DONE 配置结束信号。

电源管脚:VCCINT 内核电压。

130nm为1.5V,90nm 为1.2VVCCIO 端口电压。

一般为3.3V,还可以支持多种电压,5V、1.8V、1.5VVREF 参考电压GND 信号地时钟管脚:VCC_PLL PLL管脚电压,直接连VCCIOVCCA_PLL PLL模拟电压,截止通过滤波器接到VCCINT上GNDA_PLL PLL模拟地GNDD_PLL PLL数字地CLK[n] PLL时钟输入PLL[n]_OUT PLL时钟输出特殊管脚:VCCPD 用于寻则驱动VCCSEL 用于控制配置管脚和PLL相关的输入缓冲电压PROSEL 上电复位选项NIOPULLUP 用于控制配置时所使用的用户I/O的内部上拉电阻是否工作TEMPDIODEN 用于关联温度敏感二极管*********************************** *************************************** *******1/1.I/O,ASDO在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CS

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

1特殊管脚

2用户I/O

1并行异步模式

2串行异步模式

输入

片选择信号:nCS为低电平且CS为高电平器件被使能可以进行配置,如果只有一个芯片选择输入被使用,那么另外一个必须被激活,(举例来说:如果只用CS作为片选择信号则nCS必须被连接到地),在配置和初始化的过程中,nCS和CS管脚必须被处于有效状态,

本管脚必须通过一个1K的电阻上拉到VCCIO

(APEX 20KE或APEX 20KC器件使用10K欧姆电阻)

外部的信号源可以驱动本管脚为低,来延迟初始化的过程,当使用一个配置器件进行配置除外,

在配置以及初始化之后,驱动本管脚为低,不影响配置器件。

(详细见AN116中的配置时序)

DCLK

APEX II

1配置器件

2串行加载

3串行异步加载

输入

数据输入:对FLEX 6000器件来说串行的配置数据是出现在DATA引脚,在串行异步加载方式下,nRS信号被锁存之后DATA管脚上出现的是RDYnBSY信号;

(详细见AN116中的PSA配置时序)

DATA[7..1]

APEX II

APEX 20K

Mercury

ACEX 1K

nCONFIG

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

特殊管脚不能做用户I/O

All

输入

配置控制引脚:

由0-1的跳变开始配置,由1-0跳变则复位器件;当设定本管脚为0时,所有I/O为三态。

(详细见AN116中的配置时序)

CONF_DONE

APEX II

如果在配置过程中,如有错误发生,本管脚被器件拉;。

如果在配置或初始化过程中,有一个外部的信号源驱动本管脚为低,则器件进入一个错误的状态;

在配置或初始化之后,驱动本管脚为低,不会影响器件。但是,如果使用专用配置器件,驱动本管脚低将引起配置器件试图去配置APEX或FLEX器件。

(详细见AN116中的配置时序)

FLEX 6000

1特殊管脚

2用户I/O

串行异步模式

RDYnBSY

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

1特殊管脚

2用户I/O

1并行异步模式

2串行异步模式

输出

忙闲信号:高电平表示器件准备好来存取另外字节的数据;高电平表示器件没有准备好接收另外字节的数据。

ACEX 1K

FLEX 10K

-

级联

输出

当设备配置完成后被驱动为低电平。在多器件配置过程中,这个管脚用来连接后面器件的nCE引脚,最后一片的nCEO悬空;

FLEX 6000

I/O

nWS

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

1特殊管脚

2用户I/O

并行异步模式

输入

写选通输入:对于APEX II、Mercury、ACEX 1K、APEX 20K和FLEX 10K器件0-1的跳变引起器件锁存一个字节的数据在DATA[7..0]引脚;对于FLEX 6000器件,一个0-1的跳变会引起器件锁存一个位的数据在DATA引脚。

FLEX 10K

1特殊管脚

2用户I/O1并行异步模式 Nhomakorabea2串行异步模式

输入

数据输入:并行的字节流数据通过DATA[7..1]与DATA0输入器件;

DATA0

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

特殊管脚不能做用户I/O

配置器件

PS

PPA

PPS

输入

数据输入:在串行配置模式下比特流数据通过DATA0写入器件;

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

-

1配置器件

2串行加载

3并行同步模式

输入

时钟输入,用于从一个外部信号源输入时钟数据进入器件,在串行异步模式或并行异步模式

配置中, DCLK应当被拉高,不能悬空;

nCE

APEX II

APEX 20K

Mercury

ACEX 1K

DATA7

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

1特殊管脚

2用户I/O

PPA

输出

在PPA配置方式,DATA的数据是被RDYnBSY信号通过电平触发方式在nRS信号已经被锁存之后写入;

(详细见AN116中的PPA配置时序)

INIT_DONE

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

1器件级的使能

2用户I/O

All

输出

集电极开路

状态管脚:可以被用来指示器件已经被初始化或者已经进入用户模式;在配置过程中INIT_DONE引脚保持低电平,在初始化之前和之后,INIT_DONE引脚被释放,被上拉到VCCIO通过一个外部上拉电阻,因为INIT_DONE在配置之前是三态,所以被外部的上拉电阻拉到高电平。因此监控电路必须能够检测一个0-1的跳变信号。这个选项可以在MAX+PLUS II或Quartus II软件中被设置。

MSEL1 MSEL0配置模式

0 0串行配置或使用配置器件模式10并行同步模式

1 1并行异步模式

MSEL

FLEX 6000

特殊管脚不能做用户I/O

All

输入

MSEL配置模式

0串行加载或使用加载器件模式,及MasterBlaster或ByteBlasterMV加载电缆模式

1串行异步模式

nSTATUS

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

特殊管脚不能做用户I/O

All

双向

集电极开路

上电后被器件拉低,在5US之内,被器件释放,

(当使用一个专用配置器件时,专用加载器件将控制这个脚为低长达200ms。)这个管脚必须通过一个1K电阻上拉到VCCIO;

(APEX 20KE或APEX 20KC器件为10K欧姆)

FLEX 10K

FLEX 6000

-

All

输入

低有效芯片使能,本管脚使用低电平使能器件来允许配置,对于单芯片配置应当被固定为低电平,在配置以及初始化过程和用户模式,本管脚必须固定为低电平;在级联时,第一片的nCE接地,前一片的nCEO接后一片的nCE;

nCEO

APEX II

APEX 20K

Mercury

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

特殊管脚不能做用户I/O

All

双向

集电极开路

状态输出:

在配置之前和配置过程中,器件驱动本管脚为0,一旦所有配置数据都被接收并没有错误发生,则初始化时钟周期开始时器件释放本管脚;

状态输入:在所有数据被接收后,本管脚为高电平,器件初始化,然后进入用户模式;

DEV_OE

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

1器件级的使能

2用户I/O

All

输入

此管脚需要在编译设置中设定才能实现第一功能,缺省是第二功能;

当本引脚被拉低,所有I/O都是三态。

当本引脚被拉高,所有I/O在正常的程序控制状态。

DEV_CLRn

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

1JTAG

2用户管脚

All

输入

JTAG引脚。当被用作为用户I/O引脚的时候,

JTAG引脚电平必须保持稳定,在配置之前和配置过程中。JTAG引脚稳定性可以预防意外的装载JTAG指令。

TDO

输出

TMS

输入

TCK

输入

ALTERA FPGA特殊管脚说明、

管脚名称

器件系列

使用模式

配置模式

管脚类型

描述

MSEL0

MSEL1

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

特殊管脚不能做用户I/O

All

输入

设置APEX II、Mercury、ACEX 1K、APEX 20K和FLEX 10K器件配置模式

CLKUSR

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

1特殊管脚

2用户I/O

All

输入

可选的用户时钟输入信号:用在初始化过程中;

(注:在初始化过程中可以继续使用配置数据用的DCLK,或者切换到用CLKUSR)

DATA

FLEX 6000

特殊管脚不能做用户I/O

APEX II

APEX 20K

Mercury

ACEX 1K

FLEX 10K

FLEX 6000

1器件级的清零

2用户I/O

All

输入

此管脚需要在编译设置中设定才能实现第一功能,缺省是第二功能;